96 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 6: GTP Transmitter (TX)

R

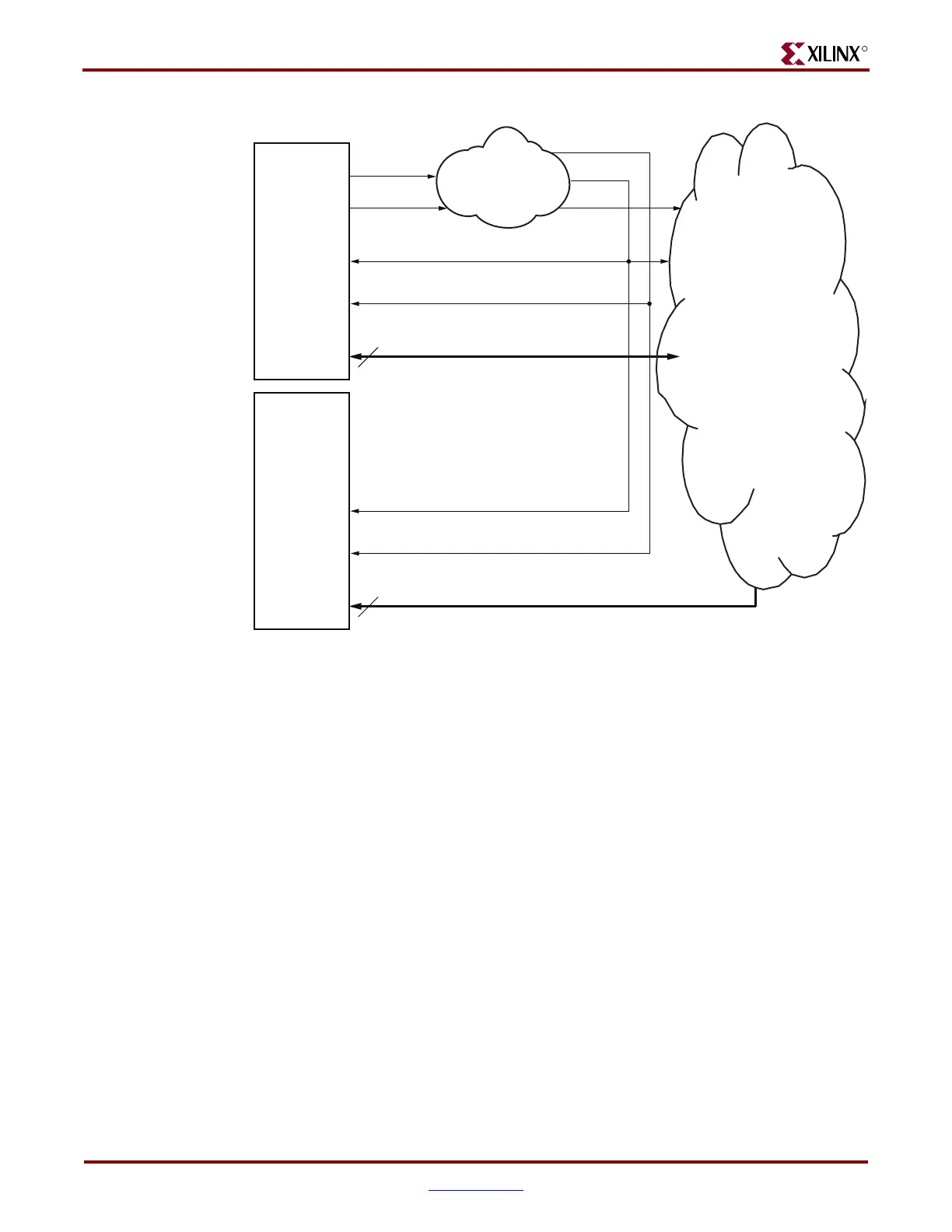

REFCLKOUT Driving Multiple Transceivers with a 2-Byte Interface

Figure 6-8 shows how REFCLKOUT can be used to generate USRCLK signals.

REFCLKOUT runs continuously, even when the GTP_DUAL tile is reset; however, extra

clocking resources might be needed to generate the correct USRCLK frequency. In

Figure 6-8, a PLL is used to generate the TXUSRCLK and TXUSRCLK2 frequencies from

REFCLKOUT. A DCM can be used instead of the PLL, but the PLL is more convenient

when the REFCLKOUT rate is not an integer multiple of the required TXUSRCLK rates.

Figure 6-7: TXOUTCLK Drives Multiple GTP Transceivers with a 2-Byte Interface

GTP

Transceiver

PLLLKDET

TXOUTCLK LOCKED

TXUSRCLK2

TXUSRCLK

TXDATA (16 or 20 bits)

GTP

Transceiver

TXUSRCLK2

TXUSRCLK

TXUSRCLK

TXUSRCLK2

TXDATA (16 or 20 bits)

Selected

Divide-by-2

Solution

UG196_c6_07_040709

Design in

FPGA

Loading...

Loading...