Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 163

UG196 (v1.3) May 25, 2007

Configurable RX Elastic Buffer and Phase Alignment

R

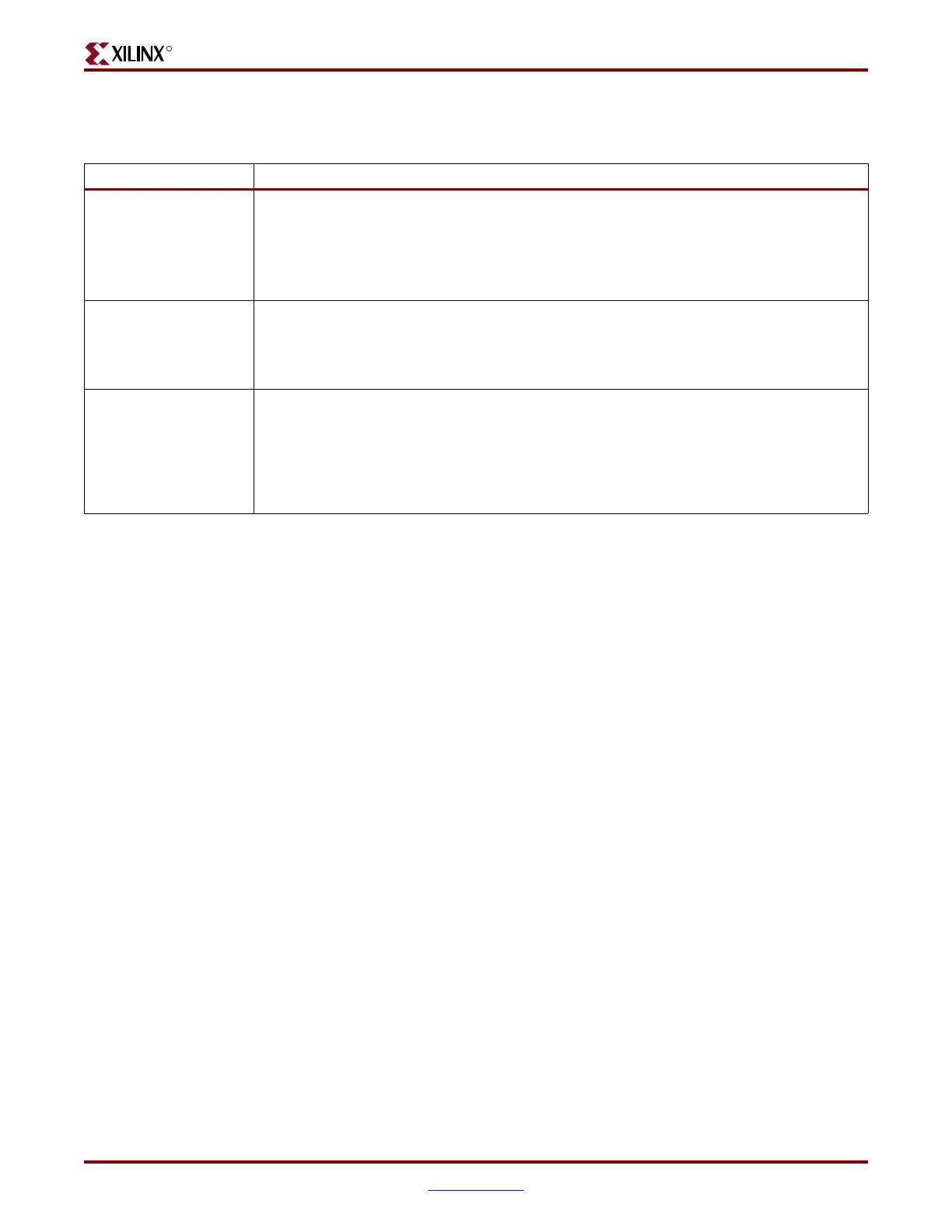

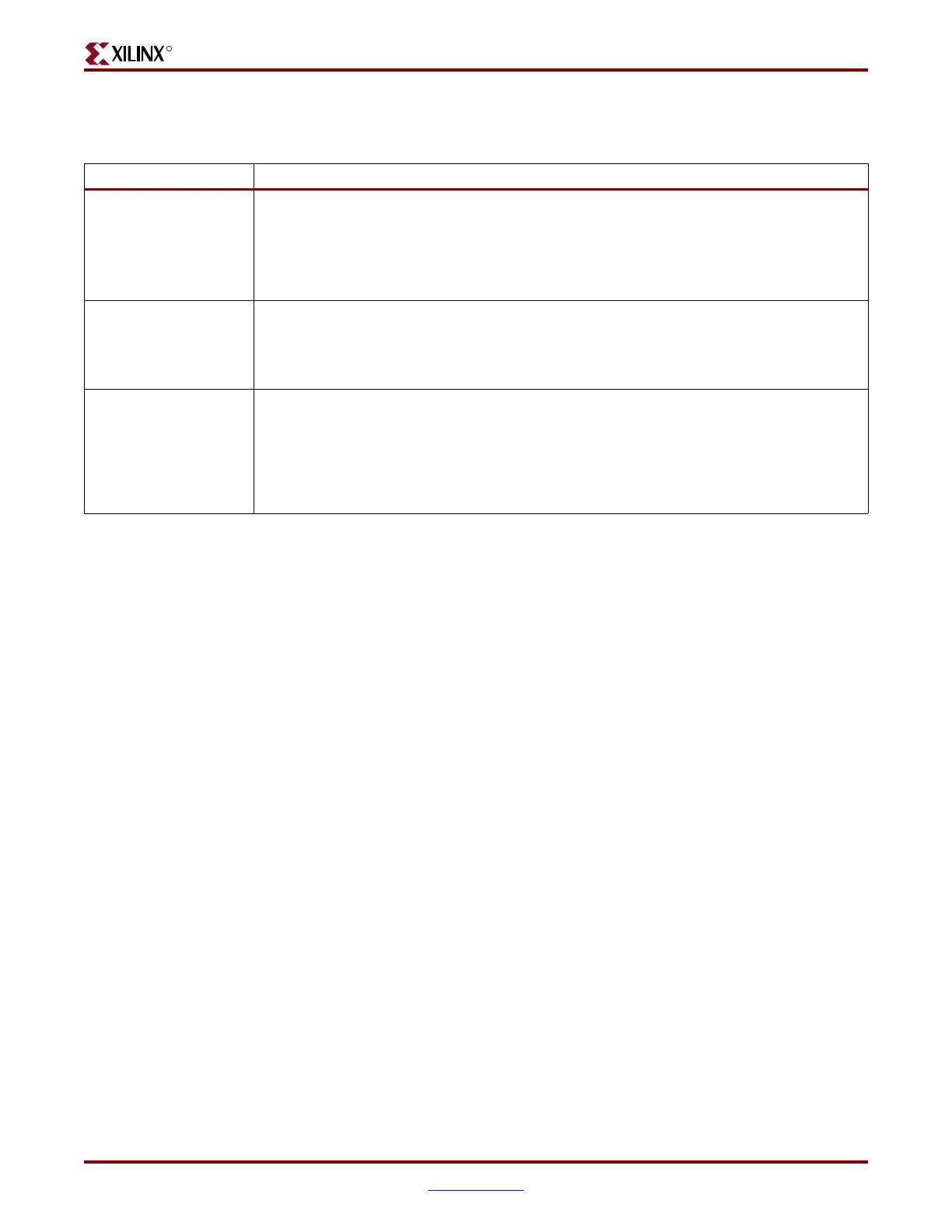

Table 7-29 defines the RX elastic buffer and phase-alignment attributes.

Description

Using the RX Buffer

Figure 7-21 shows how the RX buffer bridges the PMA Parallel clock domain (XCLK) and

the PCS Parallel clock domain (RXUSRCLK) in the RX datapath. This bridging is necessary

because there is no guaranteed phase relationship between the parallel clock from the SIPO

(XCLK) and the parallel clocks from the FPGA logic (RXUSRCLK and RXUSRCLK2).

Table 7-29: RX Elastic Buffer and Phase-Alignment Attributes

Attribute Description

OVERSAMPLE_MODE

Enables built-in 5x digital oversampling. Applies to both transceivers in the GTP_DUAL tile.

TRUE: Built-in 5x oversampling enabled

FALSE: Built-in 5x oversampling disabled

TX_BUFFER_USE must be true when OVERSAMPLE_MODE is TRUE. See “Oversampling,”

page 143 for the remaining configuration steps required to use oversampling.

RX_BUFFER_USE_0

(1)

RX_BUFFER_USE_1

(1)

Use or bypass the RX elastic buffer.

TRUE: Use the RX elastic buffer (normal mode).

FALSE: Permanently bypass the RX elastic buffer. If OVERSAMPLE_MODE is FALSE, RX

phase alignment must be used whenever the RX buffer is bypassed.

RX_XCLK_SEL_0

RX_XCLK_SEL_1

Selects which clock is used to drive the RX parallel clock domain (XCLK).

“RXREC”: (default) XCLK domain driven by recovered clock from CDR. When

OVERSAMPLE_MODE is TRUE, the recovered clock is sourced from the Oversampling

block.

“RXUSR”: RXUSRCLK port drives RX parallel clock domain. Use this mode when

bypassing the RX buffer.

Notes:

1. When the RX buffer is bypassed, 10-bit internal data width is necessary, therefore, INTDATAWIDTH = 1.

Loading...

Loading...