74 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 5: Tile Features

R

Description

GTP Reset in Response to Completion of Configuration

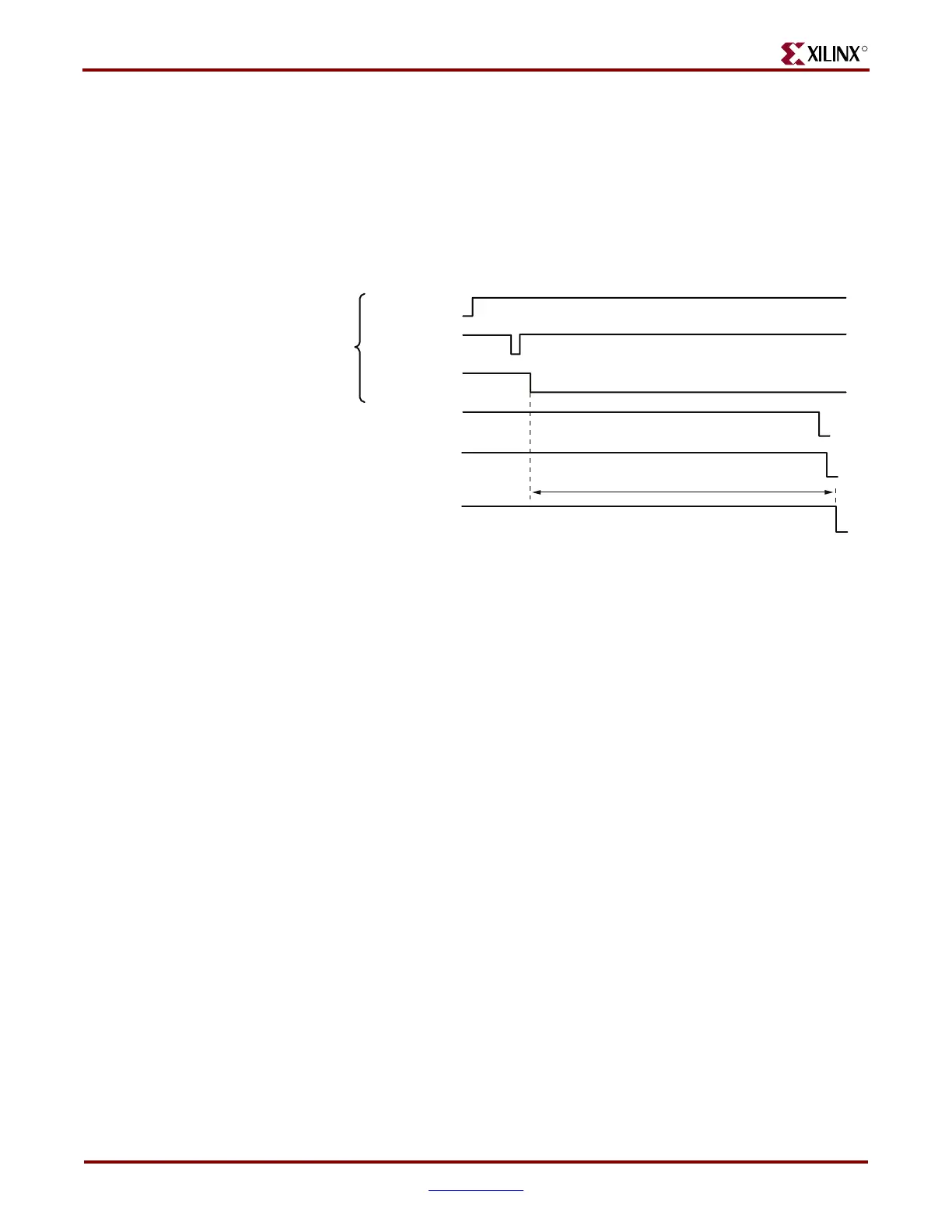

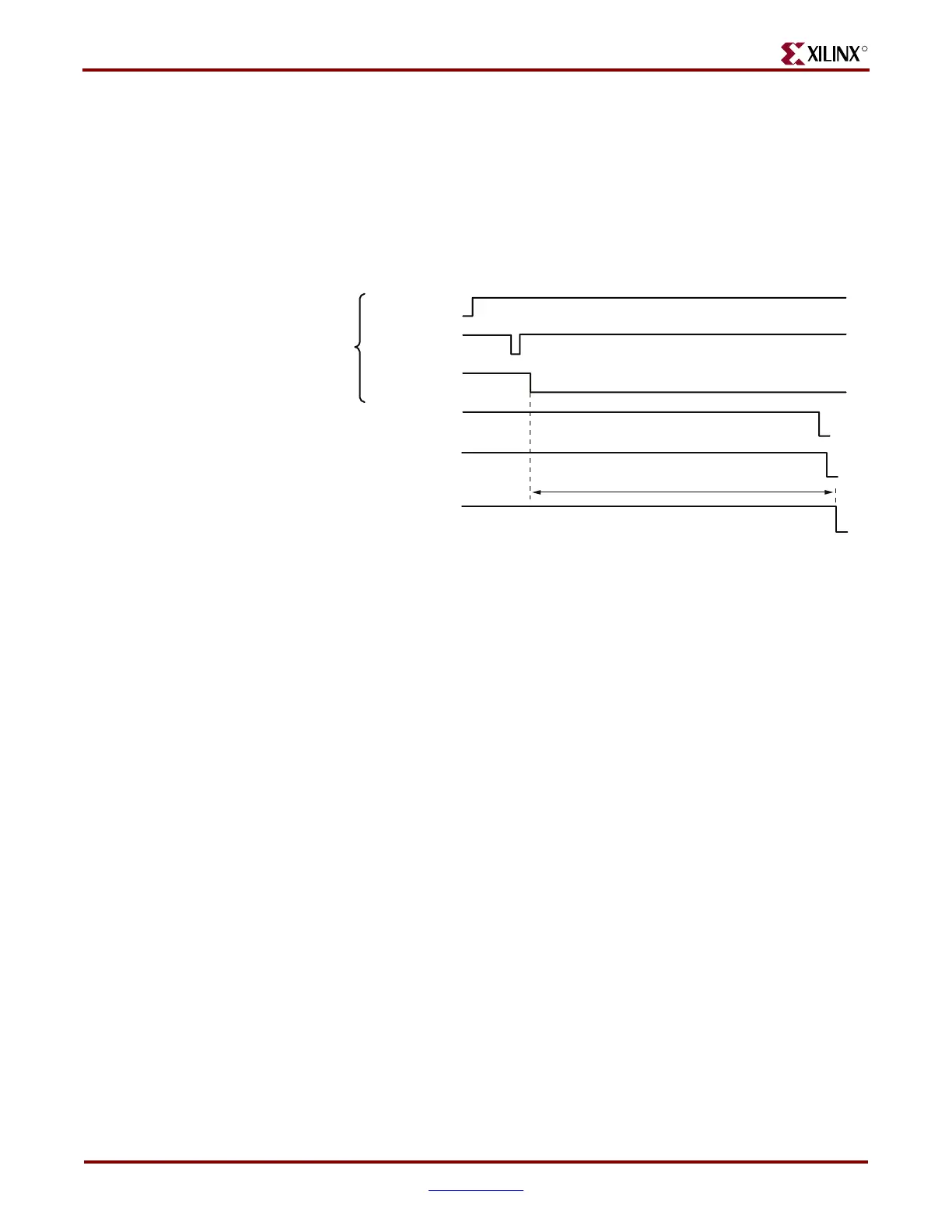

Figure 5-7 shows the GTP_DUAL reset sequence following completion of configuration of

a powered-up GTP_DUAL tile. The same sequence is activated any time

PLLPOWERDOWN goes from High to Low during normal operation.

Refer to “Power Control,” page 81 on power-down for details about PLLPOWERDOWN.

The following GTP_DUAL sections are affected by the reset sequence after configuration:

• Shared PLL

• GTP0 transmit section (PMA and PCS)

• GTP0 receive section (PMA and PCS)

• GTP1 transmit section (PMA and PCS)

• GTP1 receive section (PMA and PCS)

Figure 5-7: GTP_DUAL Reset Sequence Following Configuration

cfg_reset_b

grestore_b

gwe_b

Internal TXRESET

Global

Configuration

Signals

~160 μs

Internal RXRESET

Internal RXBUFRESET

(1)

UG196_c5_07_100606

Notes:

1. The timing of the reset sequencer inside the GTP_DUAL tile depends on the frequency of CLK25.

The estimates given in this figure assume that the frequency of CLK25 is 25 MHz.

Loading...

Loading...