162 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 7: GTP Receiver (RX)

R

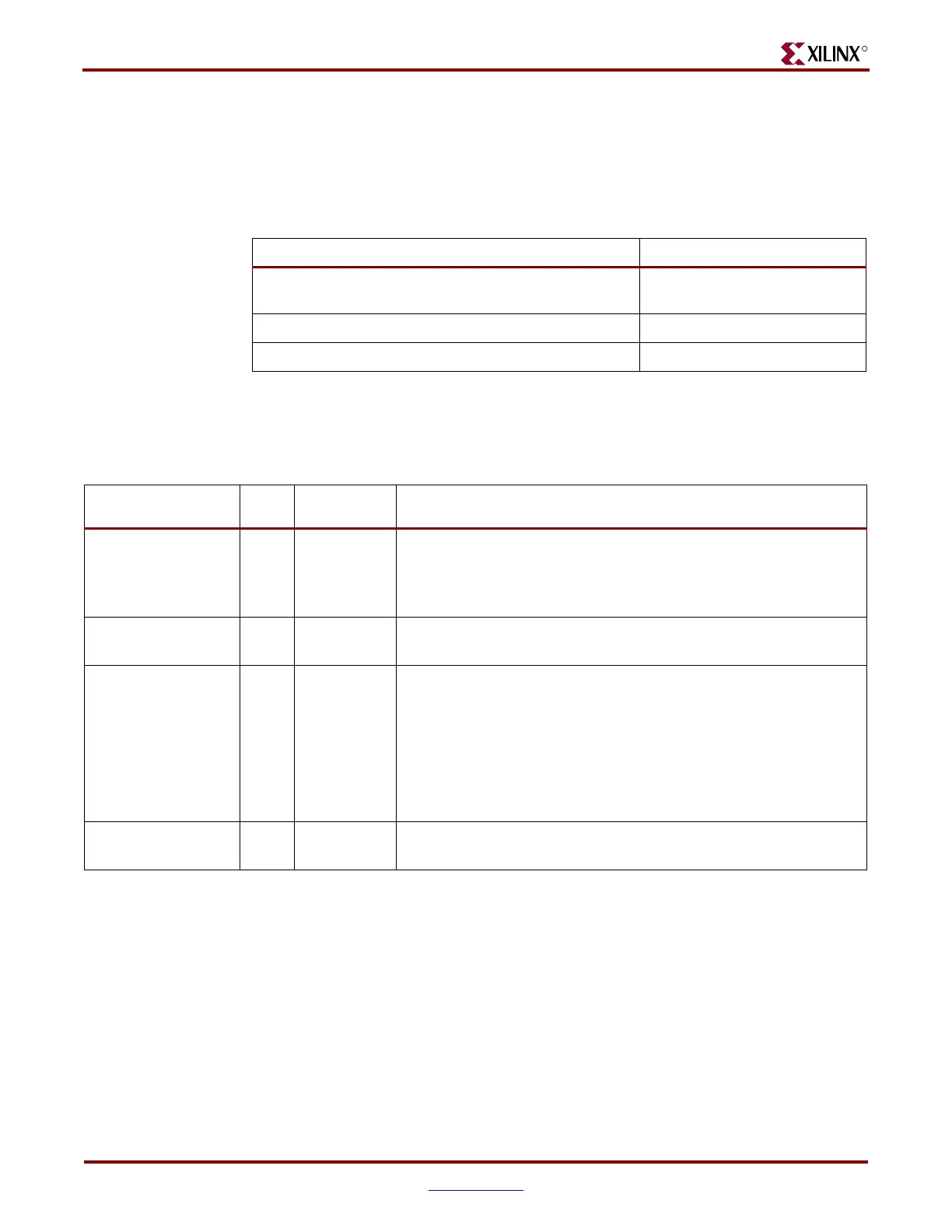

The elastic buffer is also used for clock correction (see “Configurable Clock Correction,”

page 168) and channel bonding (see “Configurable Channel Bonding (Lane Deskew),”

page 175). Clock correction is used in cases where PMACLK and RXUSRCLK are not

frequency matched. Table 7-27 lists common clock configurations and shows whether they

require clock correction.

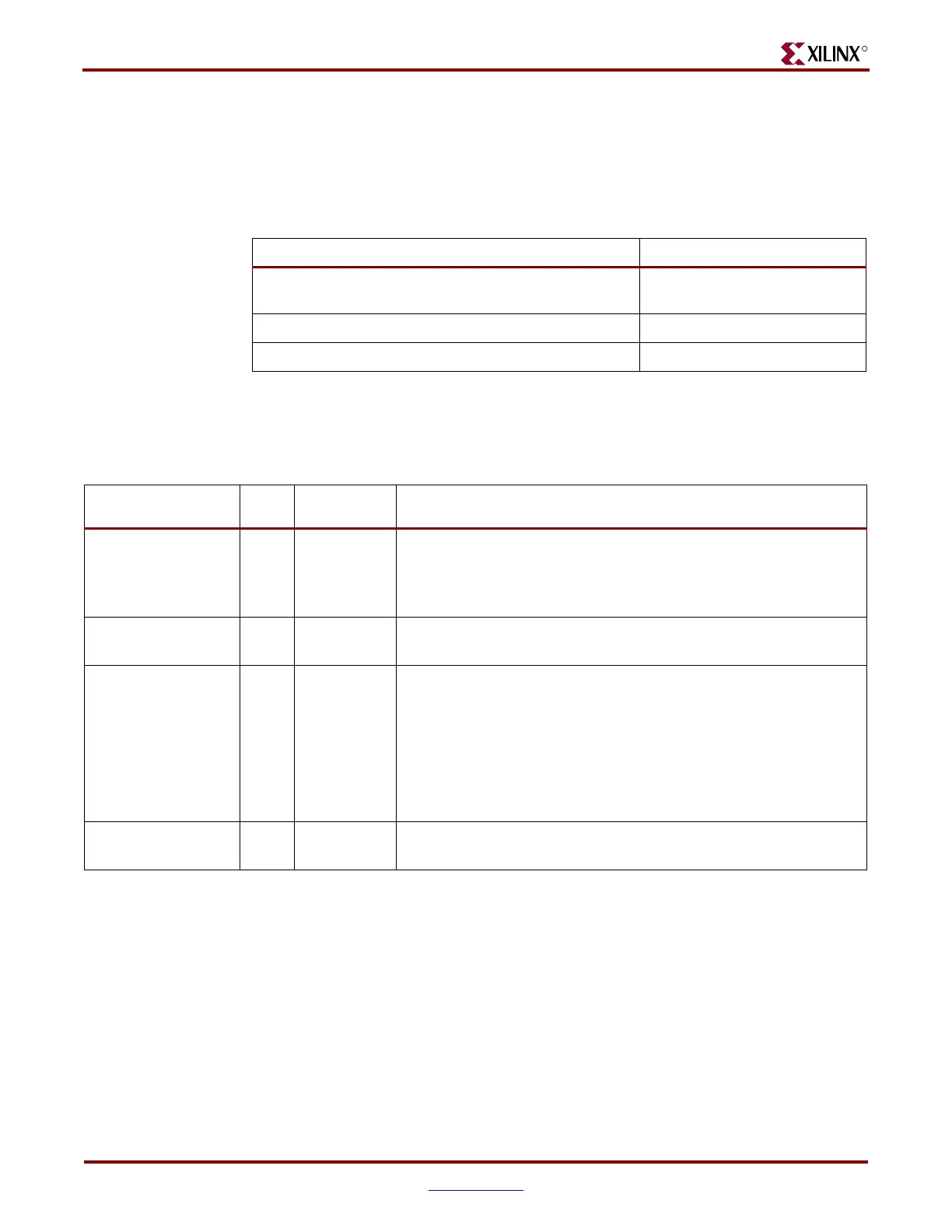

Ports and Attributes

Table 7-28 defines the RX elastic buffer and phase-alignment ports.

Table 7-27: Common Clock Configurations

Needs Clock Correction?

Synchronous System (both sides use same physical

oscillator for REFCLK)

No

Separate Reference Clocks, RX uses RXRECCLK No

Separate Reference Clocks, RX uses Local Clock Yes

Table 7-28: RX Elastic Buffer and Phase-Alignment Ports

Port Dir

Clock

Domain

Description

INTDATAWIDTH In Async

Specifies the width of the internal datapath for the entire GTP_DUAL

tile.

0: Internal datapath is 8 bits wide

1: Internal datapath is 10 bits wide

RXBUFRESET0

RXBUFRESET1

In Async Resets the RX buffer logic and re-initializes the RX buffer.

RXBUFSTATUS0[2:0]

RXBUFSTATUS1[2:0]

Out RXUSRCLK2

Indicates the status of the RX buffer as follows:

000: Nominal condition

001: Number of bytes in buffer are less than CLK_COR_MIN_LAT

010: Number of bytes in buffer are greater than

CLK_COR_MAX_LAT

101: RX Buffer Overflow

(1)

110: RX Buffer Underflow

(1)

RXPMASETPHASE0

RXPMASETPHASE1

In RXUSRCLK2

Used to align the XCLK and RXUSRCLK domains when RXUSRCLK

is driven by RXRECCLK. Allows the RXFIFO to be bypassed.

Notes:

1. If an RX buffer overflow or an RX buffer underflow condition occurs, the content of the RX buffer becomes invalid, and the RX

buffer needs re-initialization by asserting RXBUFRESET.

Loading...

Loading...