Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 81

UG196 (v1.3) May 25, 2007

Power Control

R

Power Control

Overview

The GTP_DUAL tiles support a range of power control modes. These modes support both

generic power management capabilities as well as those defined in the PCI Express and

SATA standards.

Ports and Attributes

Table 5-9 defines the power ports.

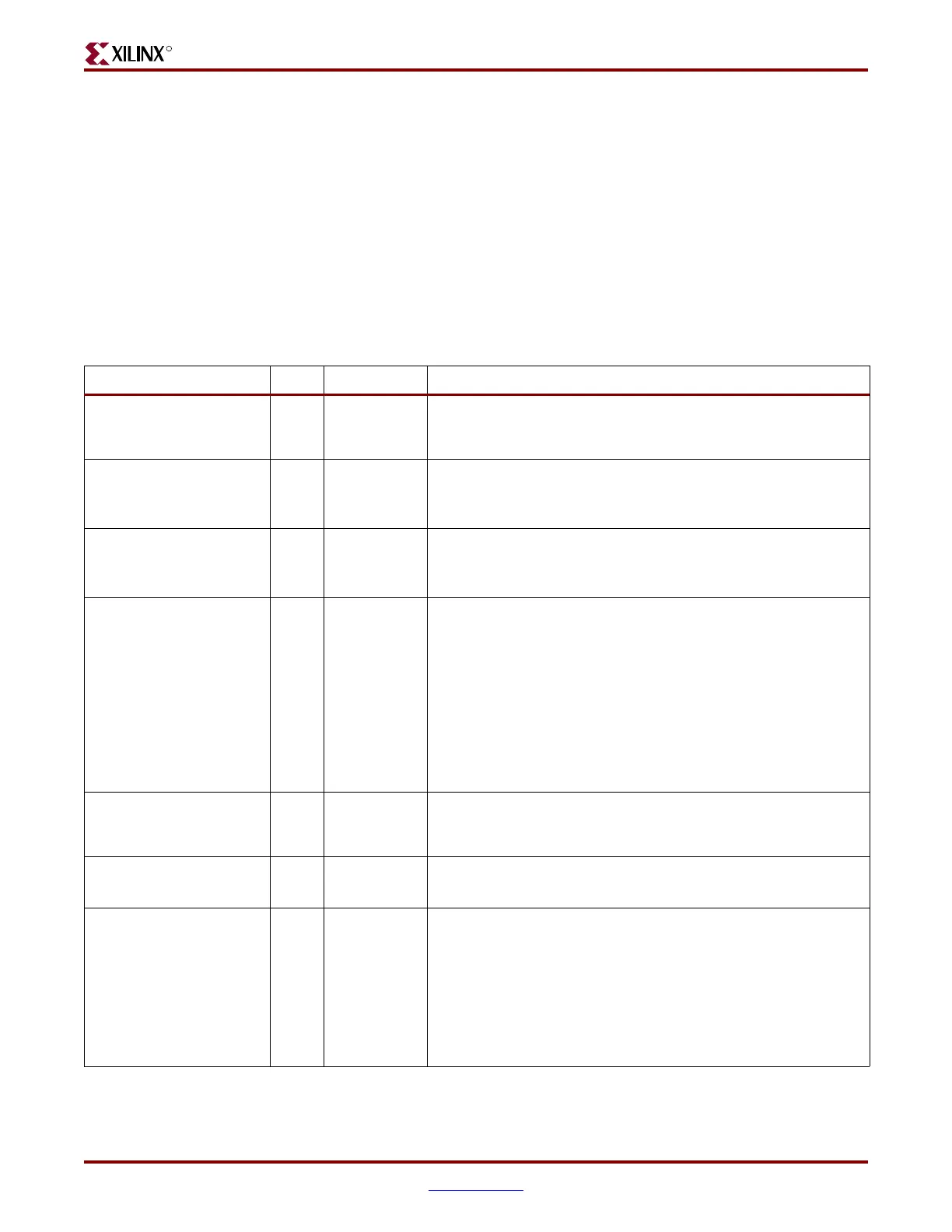

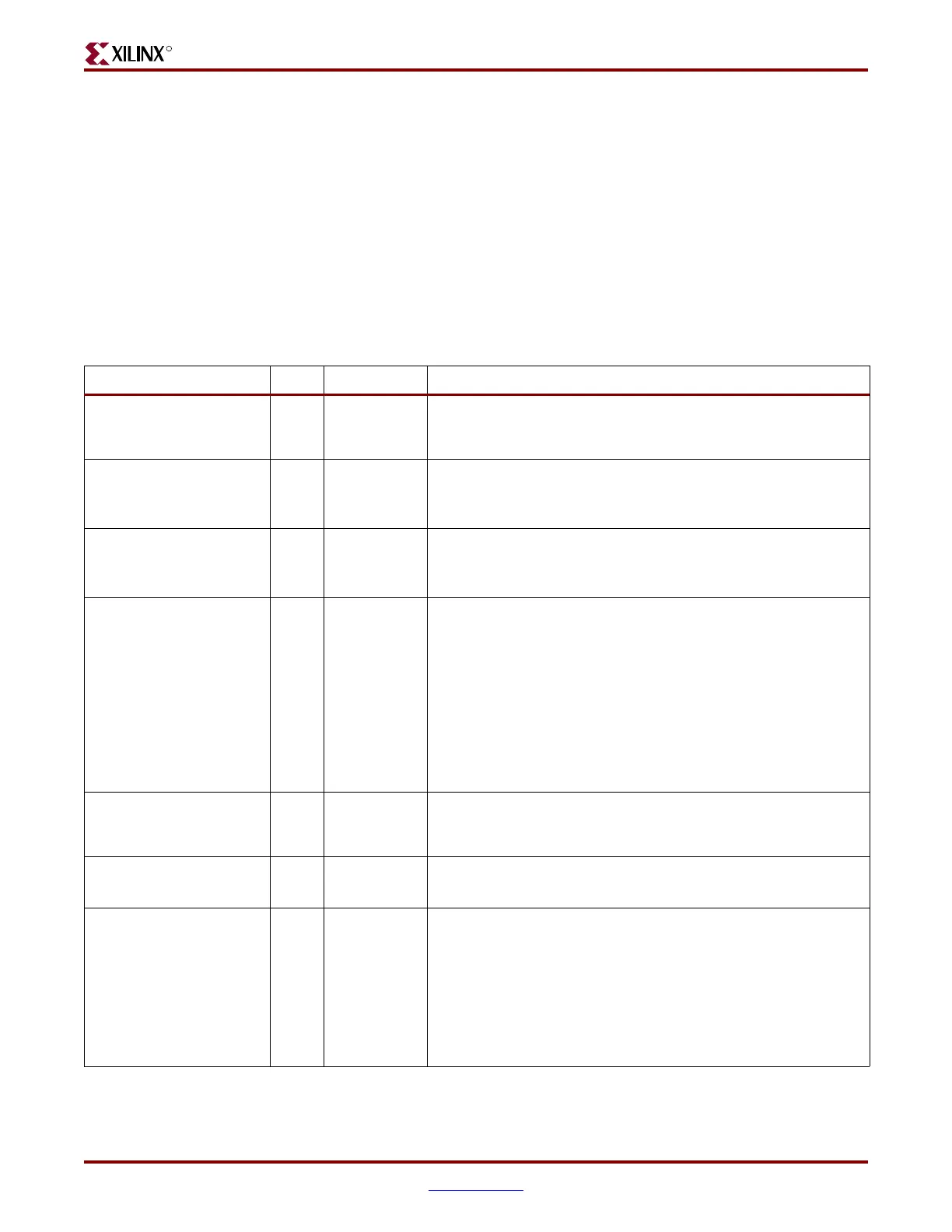

Table 5-9: Power Ports

Port Dir Domain Description

CLKIN In N/A

Reference clock input to the shared PMA PLL. The CLKIN rate in

conjunction with CLK25_DIVIDER determines the timing PCIe

powerdown state transitions.

PLLPOWERDOWN In Async

Powers down the shared PMA PLL:

0: Shared PMA PLL is powered up

1: Shared PMA PLL is powered down

REFCLKPWRDNB In Async

Powers down the GTP reference clock circuit:

0: Reference clock circuit is powered down

1: Reference clock circuit is powered up

RXPOWERDOWN0[1:0]

RXPOWERDOWN1[1:0]

In Async

Powers down the RX lanes. The encoding complies with the PCI

Express encoding. TX and RX can be powered down separately,

however, for PCI Express compliance, TXPOWERDOWN and

RXPOWERDOWN have to be used together.

00: P0 (normal operation)

01: P0s (low recovery time powerdown)

10: P1 (longer recovery time; RecDet is still on)

11: P2 (lowest power state) In the P2 powerstate, RXRECCLK

of this GTP transceiver is indeterminate, it is either a static 1 or

a static 0.

TXDETECTRX0

TXDETECTRX1

In TXUSRCLK2

Activates the receive detection sequence. The sequence ends when

PHYSTATUS is asserted to indicate that the results of the test are

ready on RXSTATUS.

TXELECIDLE0

TXELECIDLE1

In TXUSRCLK2

Drives TXN and TXP to the same voltage to perform PCI Express

electrical idle/beaconing

TXPOWERDOWN0[1:0]

TXPOWERDOWN1[1:0]

In Async

Powers down the TX lanes. The encoding complies with the PCI

Express encoding. TX and RX can be powered down separately,

however, for PCI Express compliance, TXPOWERDOWN and

RXPOWERDOWN have to be used together.

00: P0 (normal operation)

01: P0s (low recovery time powerdown)

10: P1 (longer recovery time; RecDet is still on)

11: P2 (lowest power state)

Notes:

1. Because of the shared PMA PLL, a powerdown via PLLPOWERDOWN or REFCLKPWRDNB affects both channels.

Loading...

Loading...