94 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 6: GTP Transmitter (TX)

R

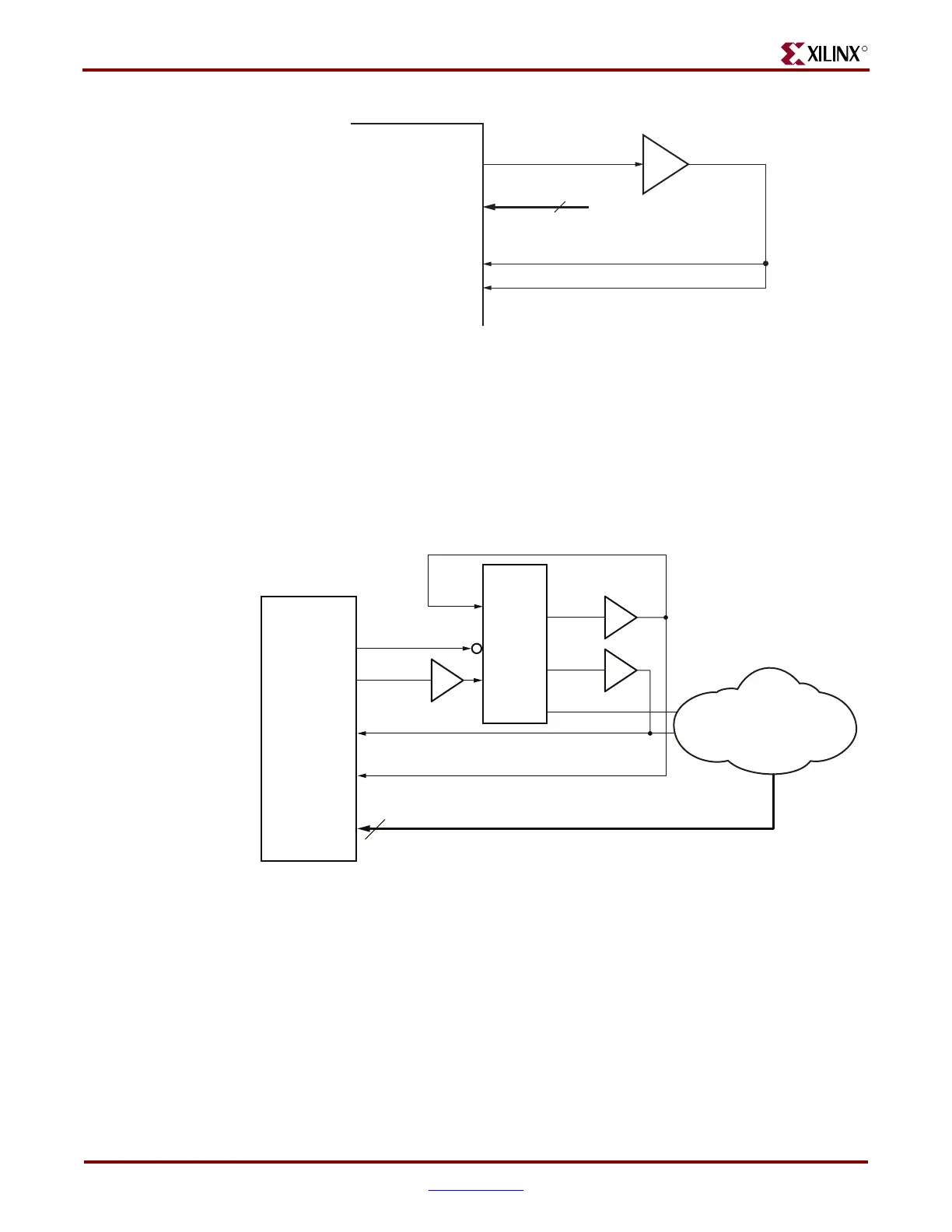

TXOUTCLK Driving GTP TX in 2-Byte Mode

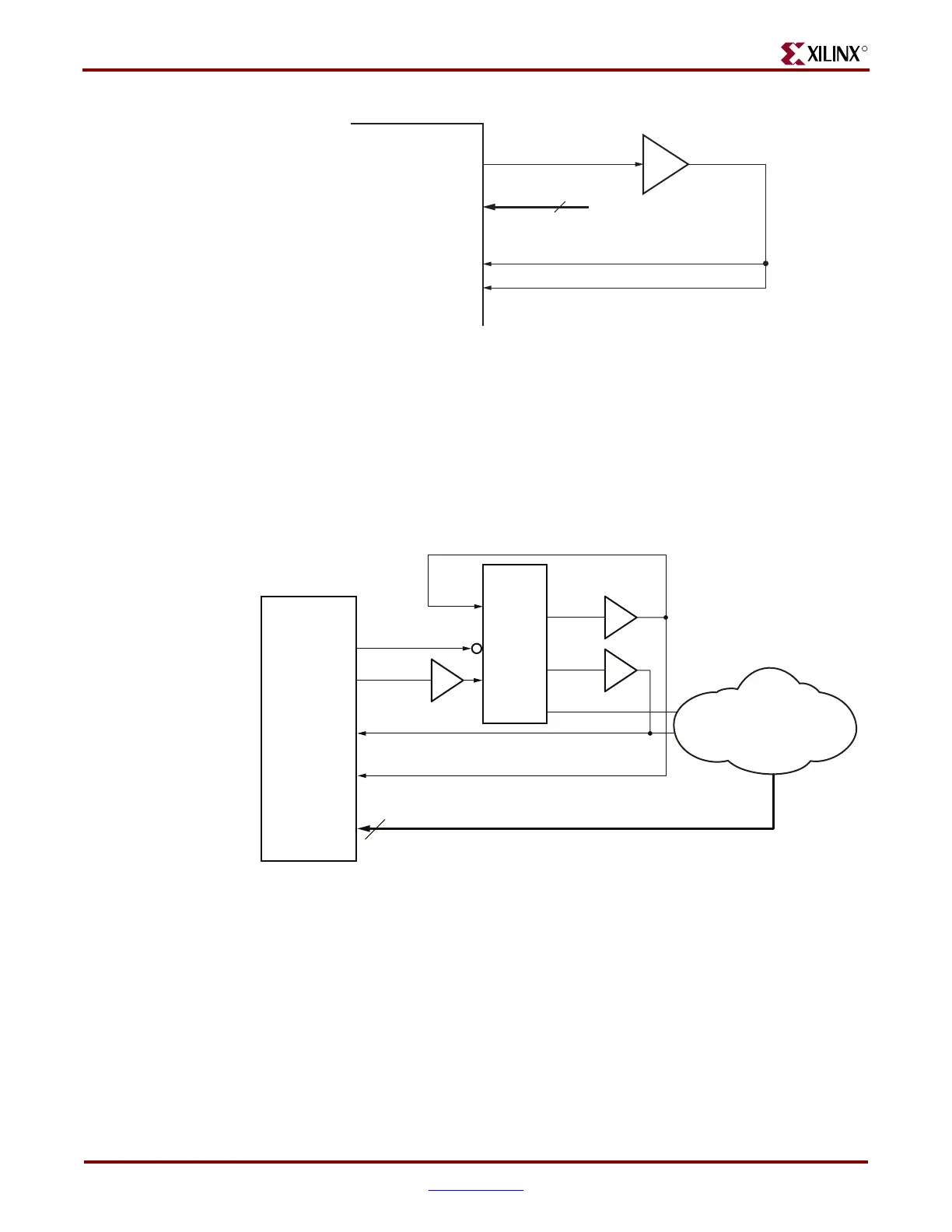

The examples in Figure 6-5 and Figure 6-6 use 2-byte datapaths (TXDATAWIDTH = 1). In

these cases, TXOUTCLK drives TXUSRCLK, and TXOUTCLK is divided by two using a

DCM or PLL to drive TXUSRCLK2.

Figure 6-4: TXOUTCLK Drives TXUSRCLK and TXUSRCLK2

GTP

Transceiver

BUFG or

BUFR

(1)

TXOUTCLK

8 or 10 Bits

TXDATA

TXUSRCLK

TXUSRCLK2

UG196_c6_04_100406

Notes:

1. Refer to the Virtex-5 Data Sheet and the Virtex-5 Configuration Guide for

the maximum clock frequency and jitter limitations of BUFR.

Figure 6-5: DCM Provides Clocks for 2-Byte Datapath

GTP

Transceiver

DCM

CLKFB

CLKIN

RST

BUFG

CLK0

PLLLKDET

TXOUTCLK

TXUSRCLK2

TXUSRCLK

TXDATA (16 or 20 bits)

CLKDV

LOCKED

Design In

FPGA

UG196_c6_05_051507

Loading...

Loading...