194 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 8: Cyclic Redundancy Check (CRC)

R

Implementation of the CRC Block

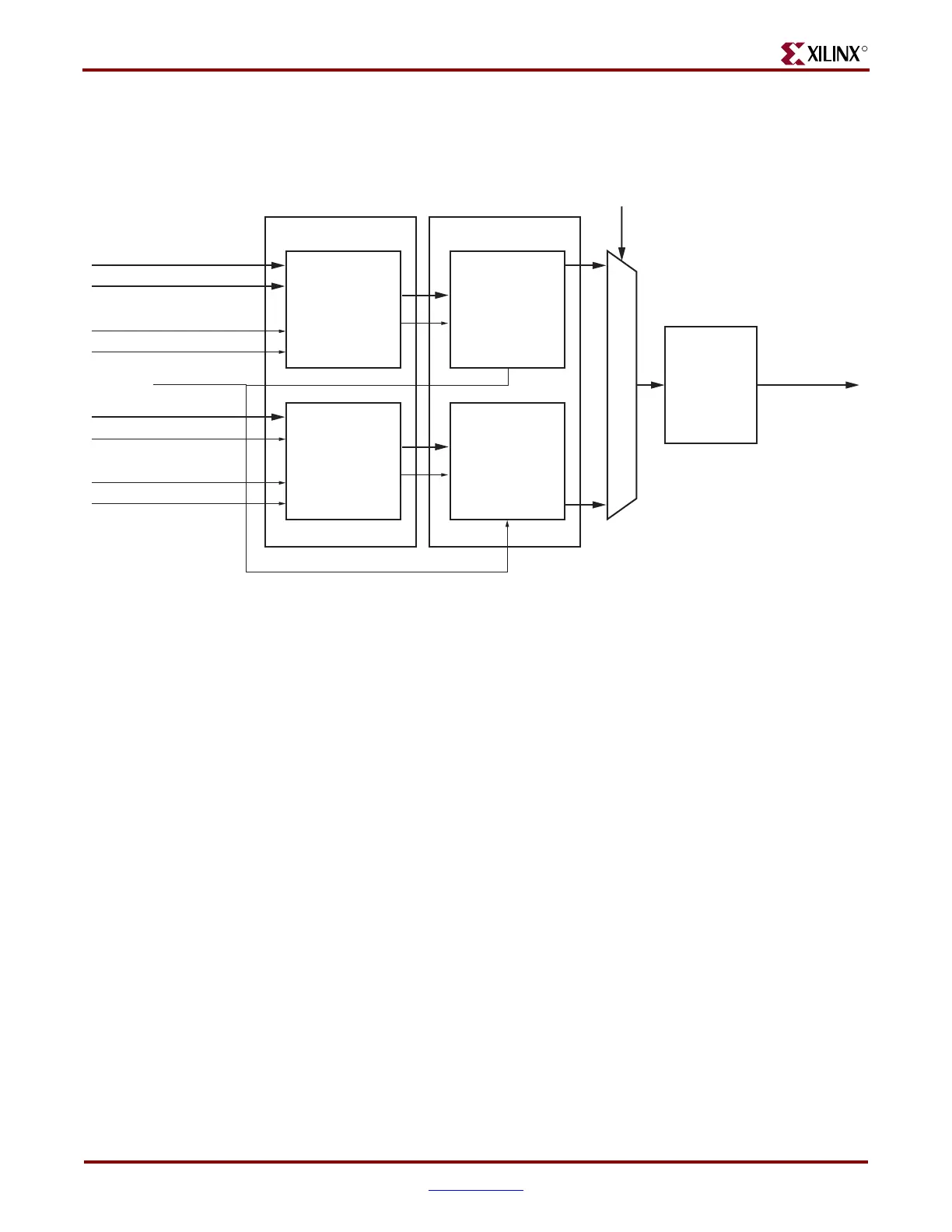

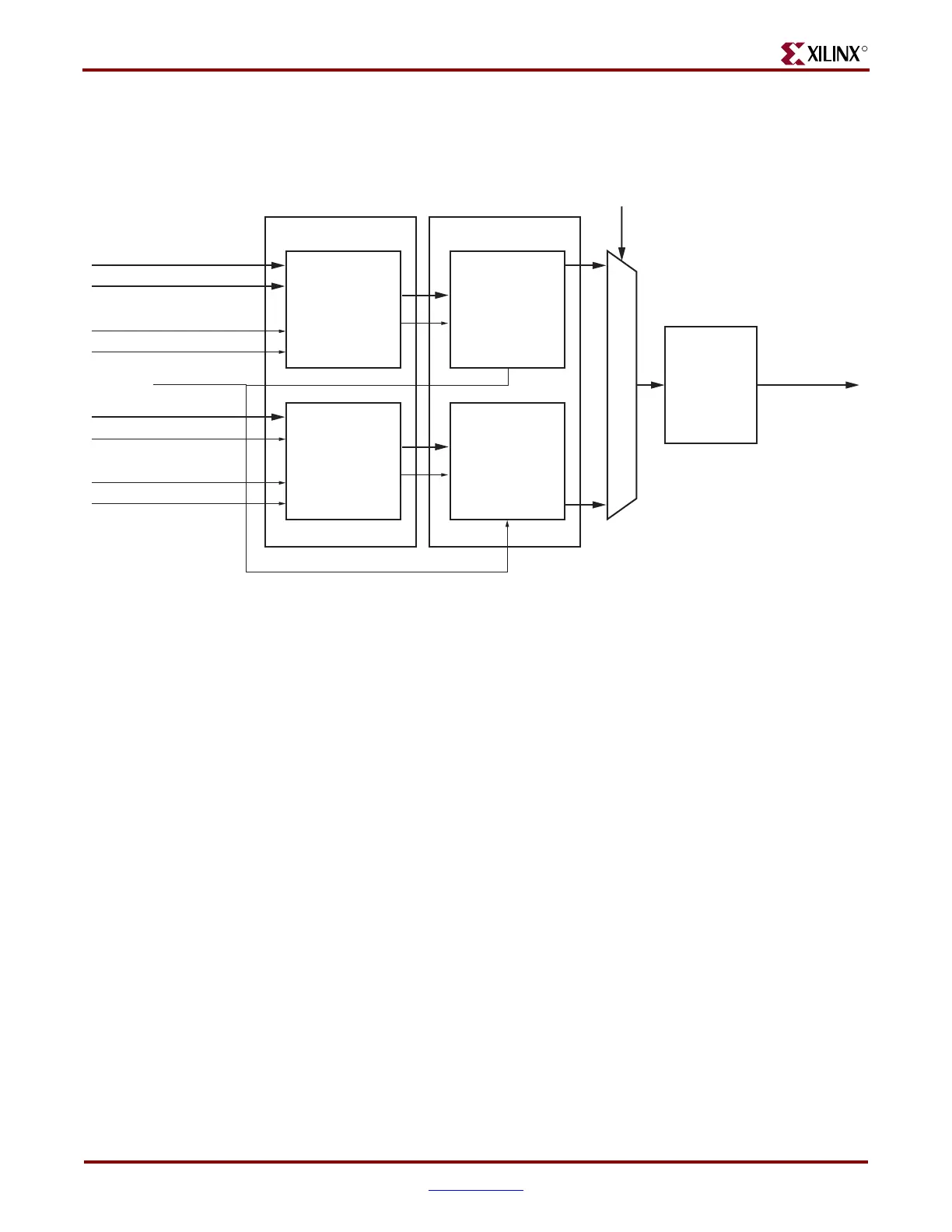

Figure 8-5 shows an implementation of the CRC.

References

Refer to XAPP209 [Ref 12] and XAPP562 [Ref 13] for more information on CRC.

Figure 8-5: CRC Implementation

CRC_CALC

(XOR Bank)

CRCOUT[31:0]

Note:

The CRCOUT is Byte Rotated

and Bit Inverted.

CRCINA[31:0]

{CRCDATAWIDTH64A, CRCDATAWIDTHA}

BANK 2_REG 1

UG196_c8_05_100506

BANK 1_REG 1

BANK 2_REGBANK 1_REG

CRCDATAWIDTH[1:0]

CRCDATAVALID

CRCCLK

CRCINB64[31:0]

CRCRESET

BANK 2_REG 2

BANK 1_REG 2

CRCDATAWIDTH64A

CRCDATAVALID

CRCCLK

Loading...

Loading...