Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 259

UG196 (v1.3) May 25, 2007

Primary Differences

R

Serial Rate Support

As the Xilinx transceivers continue to migrate, so do the supported serial rates. Table A-3

shows the rates supported by each MGT and GTP transceiver.

Encoding Support and Clock Multipliers

Protocol encoding support and clock multiplier support vary depending on the transceiver

generation. Table A-4 shows the encoding support available in each MGT and GTP

transceiver.

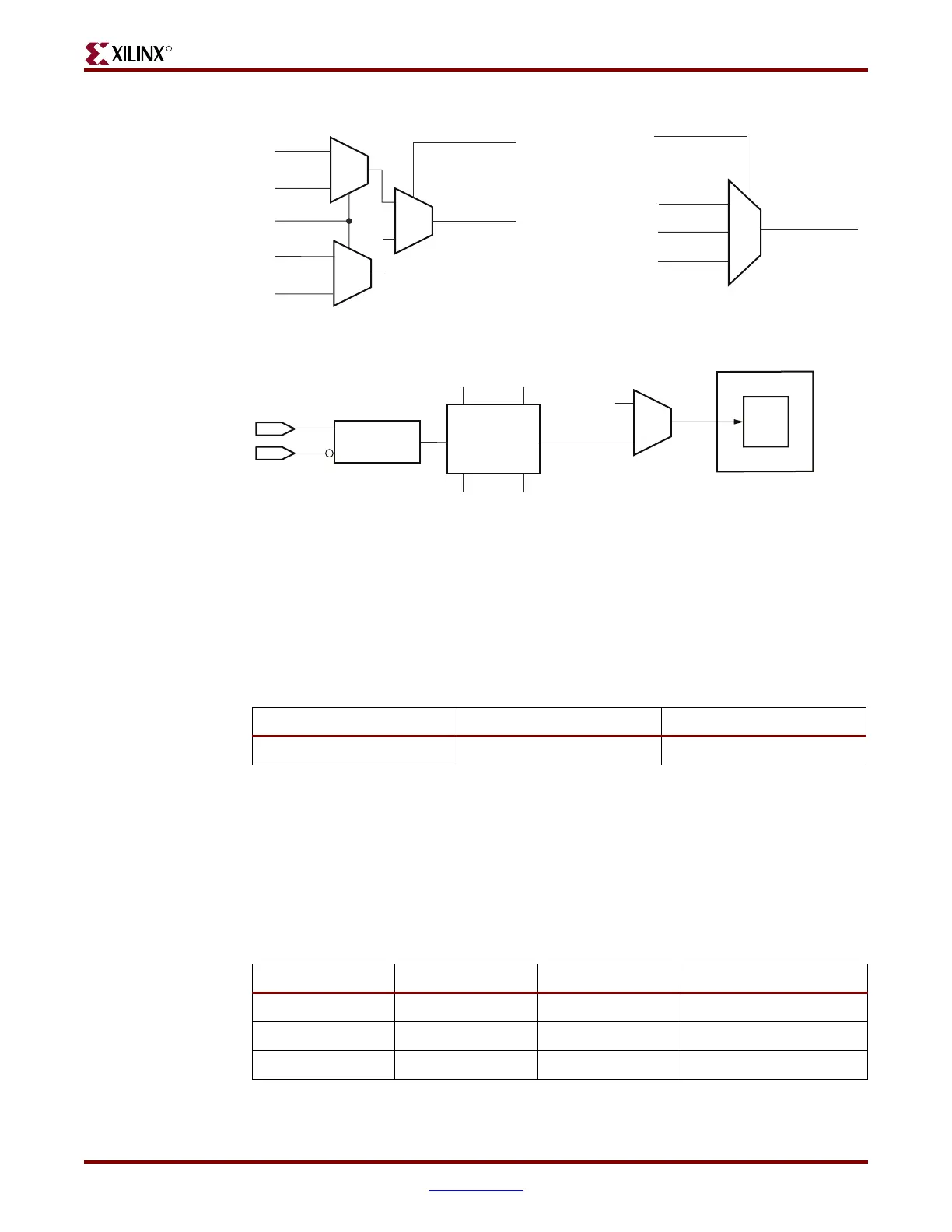

Figure A-1: Reference Clock Selection for Each Device

0

0

1

1

1.5V

2.5V

REFCLKSEL REFCLK_OUT

to PCS and PMA

REFCLK

REFCLK2

BREFCLK

BREFCLK2

REF_CLK_V_SEL

Virtex-II Pro FPGA

0

1

PMA CLKSEL

REFCLK_OUT

to PCS and PMA

REFCLK1

REFCLK2

Virtex-4 FPGA

GREFCLK

Note: All Virtex-4 clocks are differential.

UG196_a_01_011507

Virtex-5 FPGA

clkoutnorth

clkinnorth

clkinsouth

clkoutsouth

GREFCLK

GTP_DUAL Tile

PLL

IBUFDS

clkin

Dedicated

Clock

Routing

Note: Routing is controlled by software based

on the instantiated GTP_DUAL tile and

the selected clocking source

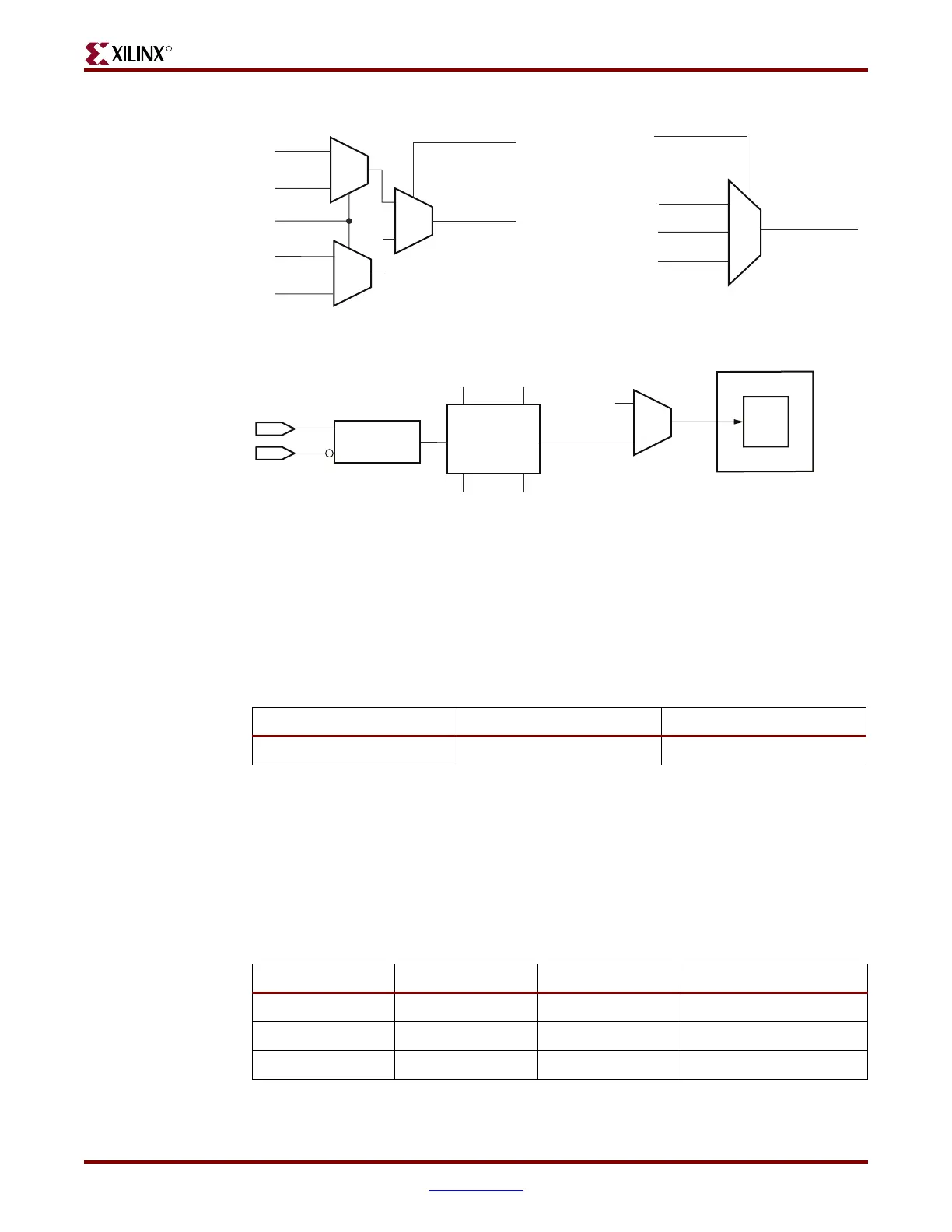

Tab le A - 3 : Serial Rate Support

Virtex-II Pro MGT Virtex-4 MGT Virtex-5 GTP Transceiver

0.622 – 3.125 Gb/s 0.622 – 6.5 Gb/s 0.100

(1)

– 3.125

Notes:

1. 100 Mb/s - 500 Mb/s with oversampling.

Tab le A - 4 : Encoding Support

Encoding Schemes Virtex-II Pro MGT Virtex-4 MGT Virtex-5 GTP Transceiver

8B/10B Yes Yes Yes

64B/66B Yes

(1)

Yes Yes

(1)

SONET Yes

(1)

Yes Yes

Loading...

Loading...