Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 191

UG196 (v1.3) May 25, 2007

Description

R

Using the CRC Blocks

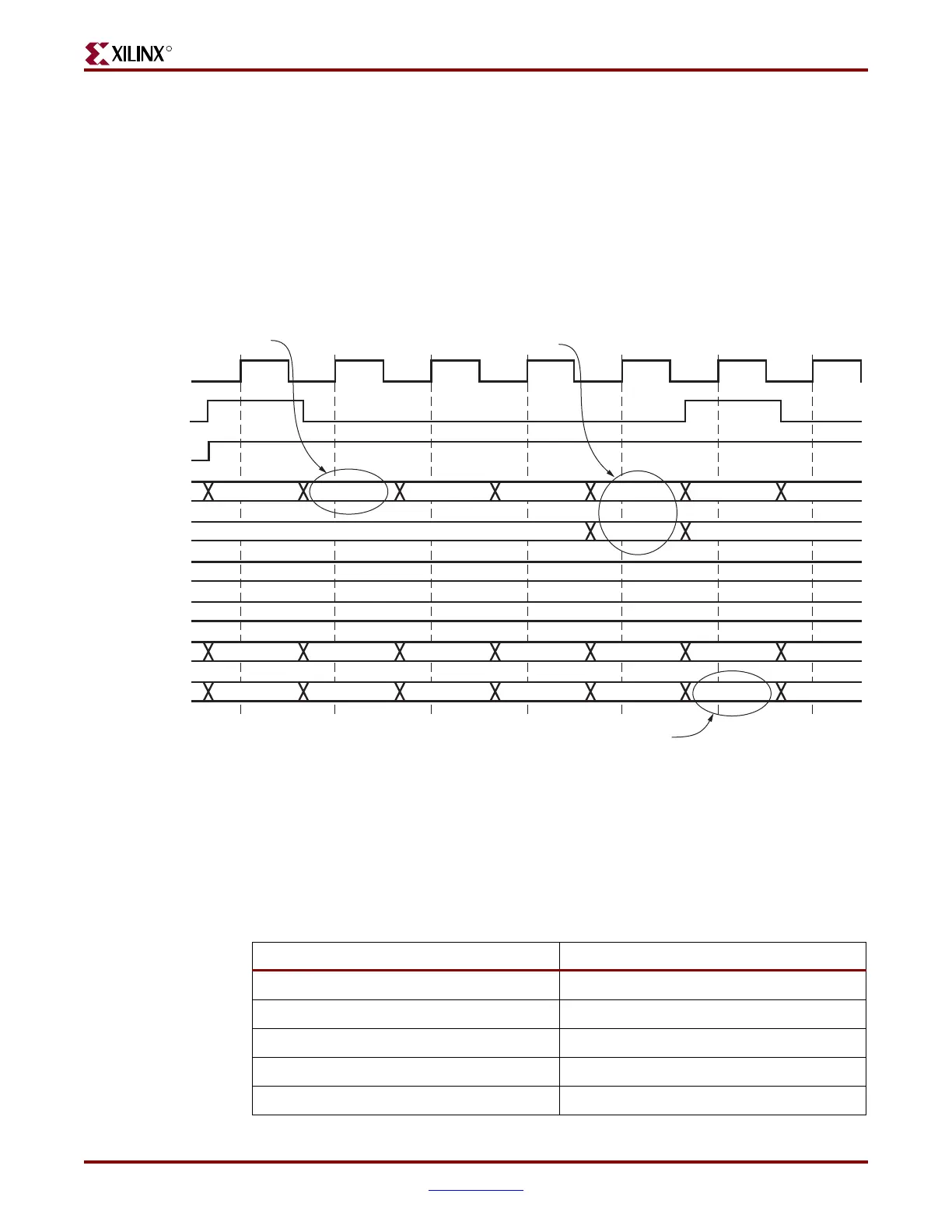

Figure 8-3 shows a CRC block calculating the CRC for input data. Also shown in this figure

is the CRC32 primitive. This operation is performed when the CRC is being generated or

checked.

In addition to the ports and attributes of the CRC32 primitive, Figure 8-3 shows two

internal signals, CRC_POLY and CRCINTREG. CRC_POLY is the fixed CRC32 polynomial

used for all calculations. CRCINTREG is an internal register that stores the CRC result after

each cycle of CRC calculation without byte reversal or bit inversion. This value is used

internally, since CRC calculations require the unmanipulated previous cycle CRC result.

At the start of each frame, CRCRESET must be applied to set the initial CRC value to

CRC_INIT. CRC calculations are cumulative, so this step is required to start the CRC

calculation at a known value. CRC_INIT is a 32-bit value for the initial state of the CRC

internal register. Its default value is 0xFFFFFFFF. The CRC_INIT value required for a

given protocol is specified as part of that protocol’s CRC algorithm. Table 8-6 shows the

CRC_INIT values for some common protocols that use the CRC32 polynomial.

Figure 8-3: Normal CRC Operation

CRCCLK

First 4 Bytes of the Frame

CRCIN

Don’t Care Don’t Care Next FrameD0

3’b011

32’hFFFFFFFF

CRC (Prev Frame)

f(CRC (Prev Frame))

CRC_INIT

f(CRC_INIT)

CRC_INIT

f(CRC_INIT)

CRC (Prev,D0)

f(CRC(Prev,D0))

CRC (Prev,D1)

f(CRC(Prev,D1))

CRC (Prev,D2)

f(CRC(Prev,D2))

CRC (Prev,D3)

f(CRC(Prev,D3))

32’h04C11DB7

3’b000 3’b011

D1 D2 D3

CRCOUT

CRCINTREG

CRC_INIT

CRC_POLY

CRCRESET

CRCDATAVALID

CRCDATAWIDTH

Last Word of the Frame -

Only CRCIN[31:24] Valid

CRC Result for the Last Valid Data of the

Frame is the CRC Result for the Frame

Notes:

1. Prev = CRCINTREG value from the previous cycle.

2. f(x) = Bit Inverted and Byte Reversed x.

UG196_c8_03_100506

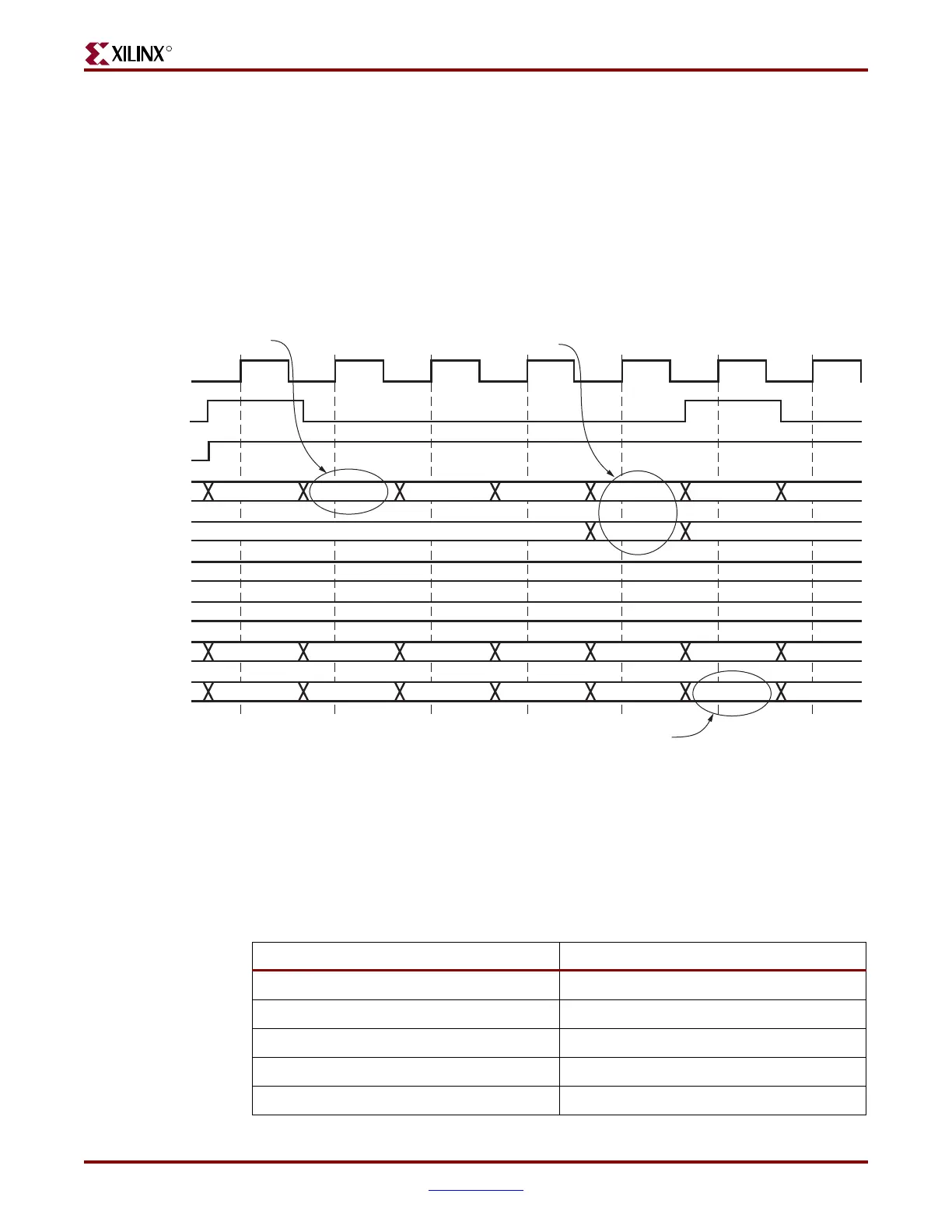

Table 8-6: CRC_INIT Values for Some Common Protocols

Protocol CRC_INIT

Ethernet 32’hFFFF_FFFF

PCI Express 32’hFFFF_FFFF

Infiniband 32’hFFFF_FFFF

Fibre Channel 32’hFFFF_FFFF

SATA 32’h5232_5032

Loading...

Loading...