192 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 8: Cyclic Redundancy Check (CRC)

R

The CRCDATAVALID port acts as a clock enable for the CRC block. If CRCDATAVALID is

High, a new CRC value is calculated every clock cycle, and the result appears on CRCOUT

after one clock cycle. If CRCDATAVALID is Low, all CRC registers hold their values from

the previous cycle.

Note:

CRCDATAVALID is called CRCDATAVALIDA on the CRC64 primitive.

CRCDATAWIDTH determines how many input data bytes are valid. Table 8-4, page 190

shows how to use CRCDATAWIDTH to set the number of valid input bytes on the CRC32

primitive. Table 8-5, page 190 shows the same for the CRC64 primitive. CRCDATAWIDTH

is usually used at the end of a frame, when not all the bytes in a data word contain valid

data. CRCDATAWIDTH can also be tied off to accommodate datapaths smaller than 32 bits

wide.

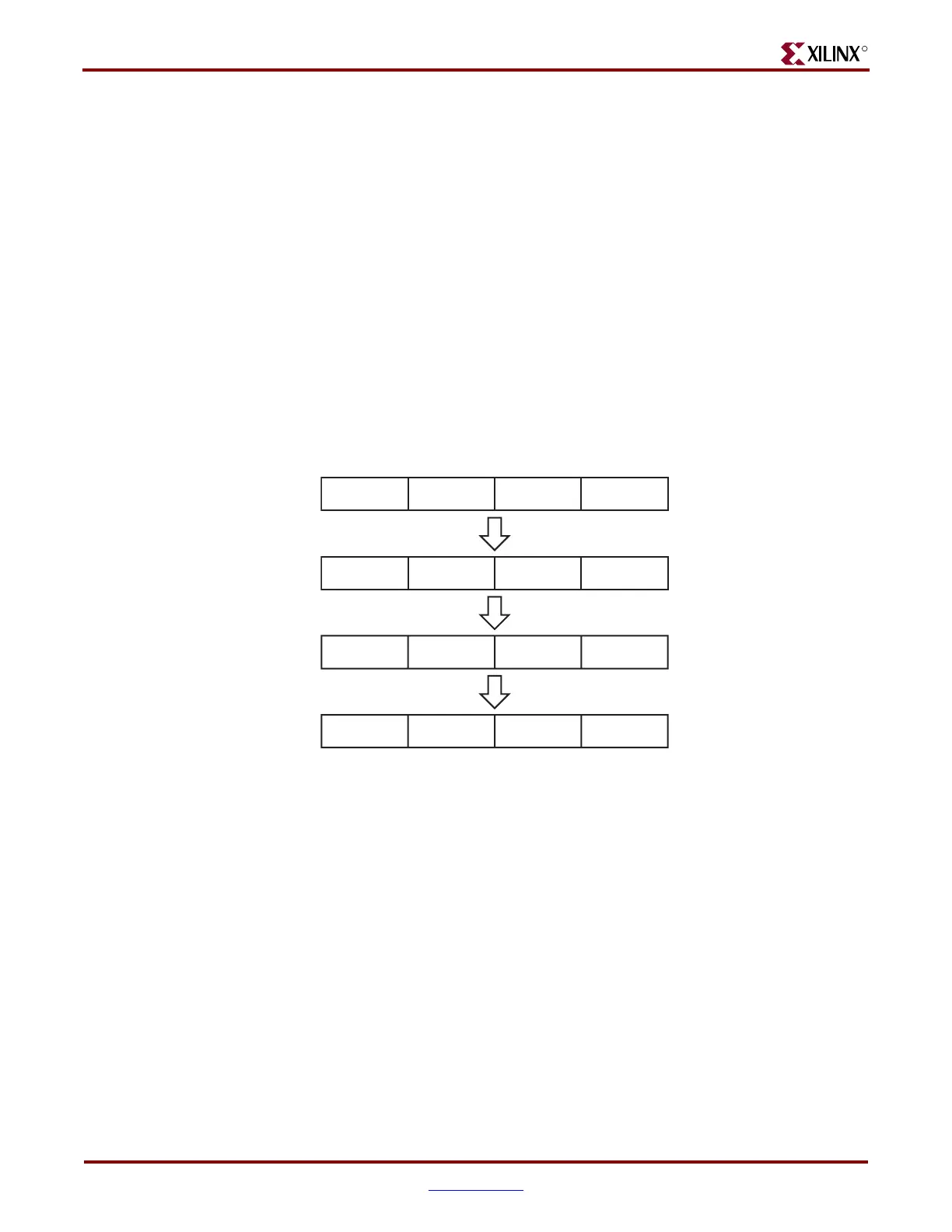

CRCOUT provides the result of the CRC calculation on the previous cycle’s data and the

previous cycle’s CRC result. In Figure 8-3, the internal CRCINTREG register shows the

raw result of the CRC calculation. CRCOUT provides the bit-inverted, byte-reversed

version of the CRC output at the same time. Figure 8-4 shows an example of the byte

rotation and bit inversion operations.

Byte rotation and bit inversion of the CRC output value are requirements for many

common protocols, so CRCOUT is provided with these operations already performed to

save FPGA resources. In designs that use a protocol that does not specify these operations

in the CRC algorithm, the user must undo these operations before using the CRC value.

The CRC result for a given frame is the CRCOUT value corresponding to the final byte(s)

of the frame. This value appears one cycle after the final byte(s) of the frame are presented

to the CRCIN port with CRCDATAVALID High.

Figure 8-4: Byte Rotation and Bit Inversion

CRCINTREG47

Byte 0

8A A4 DA

Byte 1 Byte 2 Byte 3

Bytes ReversedE2 51 25 5B

Bits Inverted1D AE DA A4

CRCOUT1D AE DA A4

UG196_c8_04_100606

Loading...

Loading...