64 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 5: Tile Features

R

See “Clocking,” page 68 for details on supplying CLKIN to the shared PMA PLL.

Examples

Configuring the Shared PLL for XAUI

The three methods to configure the shared PLL for XAUI are described below:

1. Use the RocketIO GTP Wizard.

The wizard includes a protocol file for XAUI that allows it to automatically configure

the GTP_DUAL primitive for use in a XAUI design.

2. Use the settings from Table 5-3.

Table 5-3 includes the settings for common configurations of popular protocols. XAUI

settings are included in Table 5-3, along with other protocols that use 8B/10B

encoding.

3. Use Equation 5-1 as described in the following steps:

a. Determine the required line rates.

For XAUI, both TX and RX use a line rate of 3.125 Gb/s.

b. Determine the internal datapath width.

Because XAUI is an 8B/10B-encoded standard, an internal datapath width of

10 bits is required. See “Configurable 8B/10B Encoder,” page 98 and

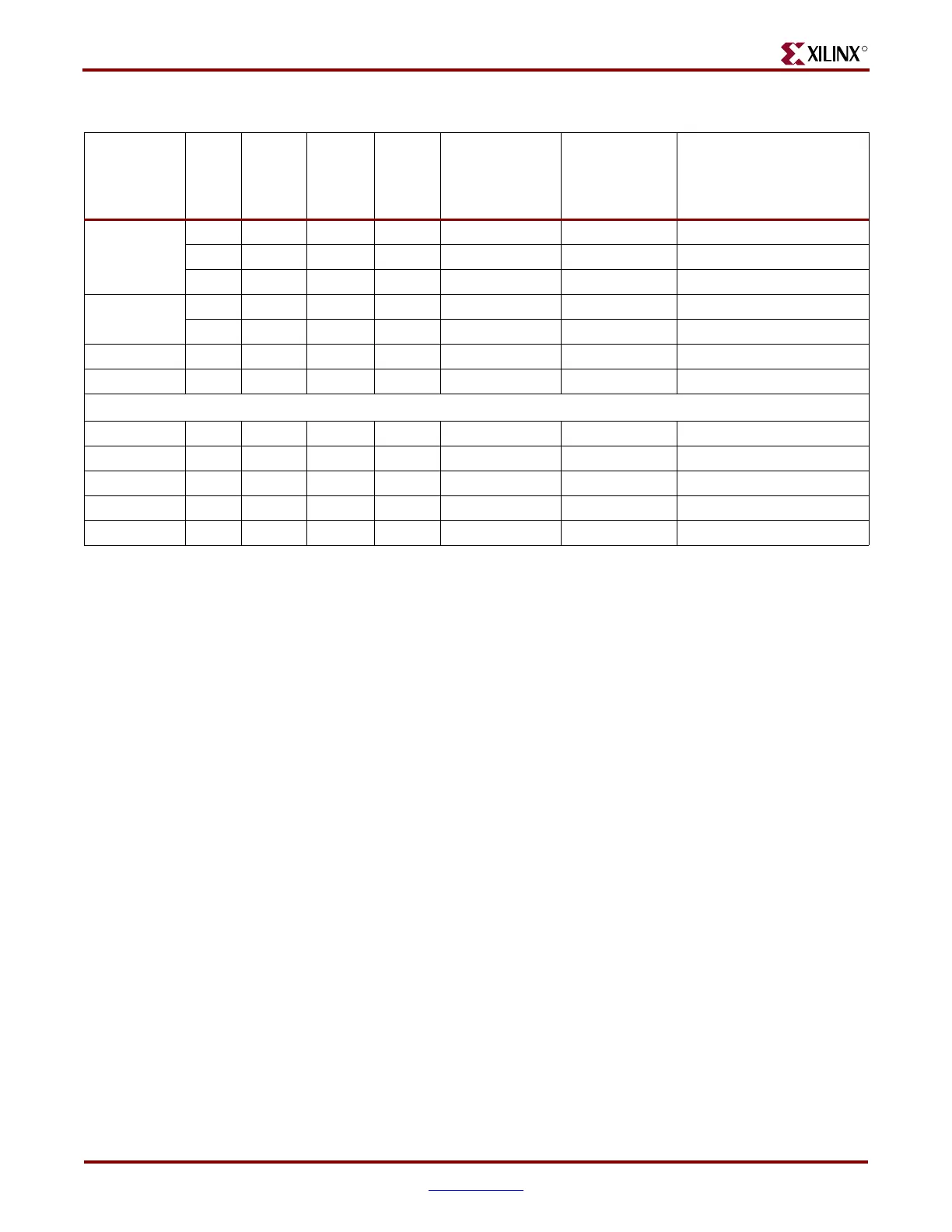

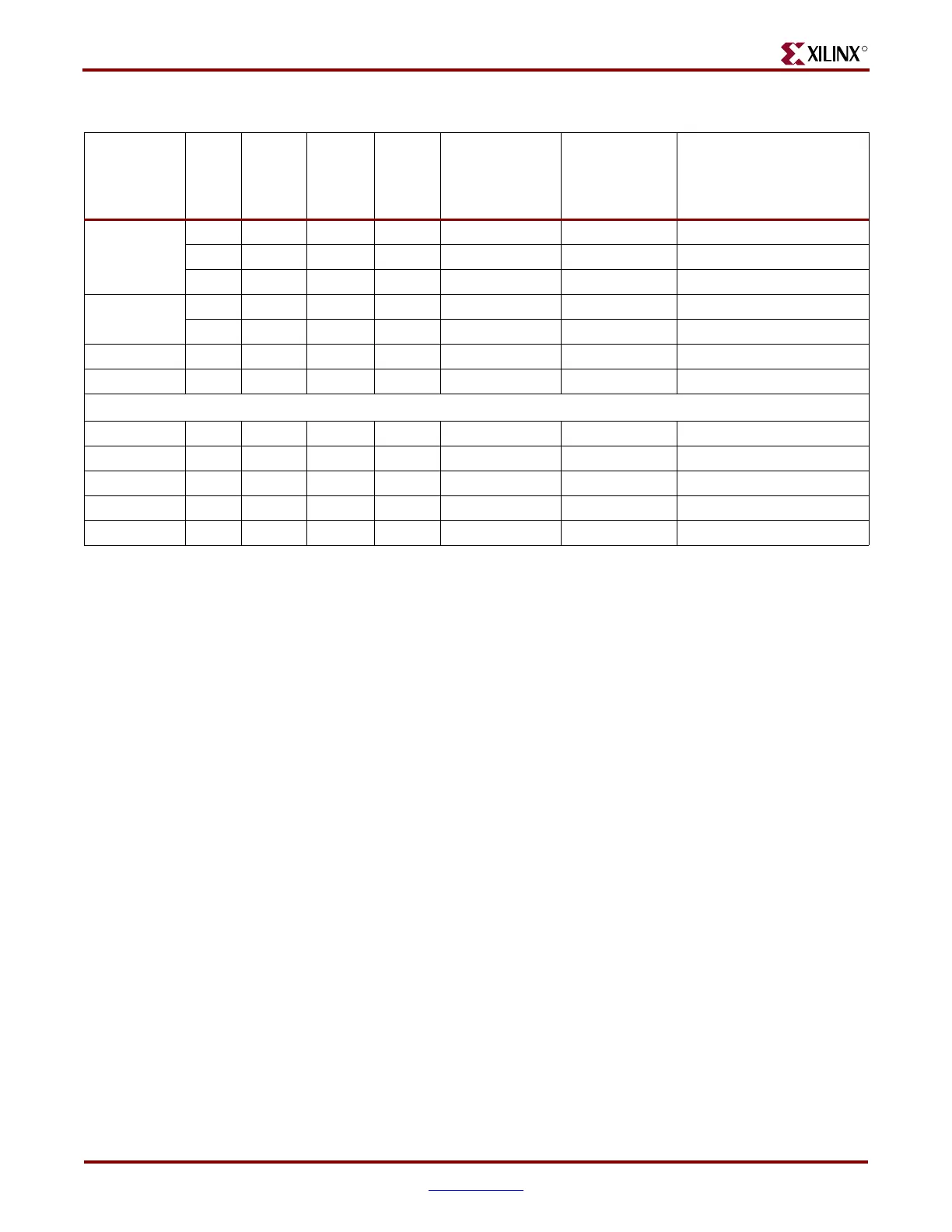

CPRI

(2)

2.4576 245.76 122.88 1.2288 1 2 1

1.2288 122.88 122.88 1.2288 1 2 2

0.6144 61.44 122.88 1.2288 1 2 4

OBSAI

(2)

1.536 153.6 153.6 1.536 1 2 2

0.768 76.8 153.6 1.536 1 2 4

SFI-5

(3)

3.125 312.5 156.25 1.5625 1 2 1

TFI-5

(3)

3.1104 311.04 155.52 1.5552 1 2 1

INTDATAWIDTH = 0 (8-bit internal datapath) → (DIV = 4)

OC12 0.62208 77.76 155.52 1.24416 1 2 4

OC48 2.488 311.04 155.52 1.24416 1 2 1

SFI-5

(3)

2.488 311.04 155.52 1.24416 1 2 1

SPI-5

(3)

2.488 311.04 155.52 1.24416 1 2 1

TFI-5

(3)

2.488 311.04 155.52 1.24416 1 2 1

Notes:

1. See “Parallel In to Serial Out (PISO),” page 110 and “Serial In to Parallel Out (SIPO),” page 141 for more details about the divider setting.

2. Synchronous system.

3. Maximum data rate.

4. Other frequency is 0.1% lower.

Table 5-3: Communication Standards (Continued)

Standard

Line

Rate

[Gb/s]

TX/RX

USRCLK

Frequency

[MHz]

Reference

Clock

Frequency

REFCLK

[MHz]

PLL Clock

Frequency

[GHz]

Reference Clock

Divider Setting

PLL_DIVSEL_REF

Feedback Loop

Divider Setting

PLL_DIVSEL_FB

Divider Settings

PLL_RXDIVSEL_OUT_(0/1)

PLL_TXDIVSEL_OUT_(0/1)

PLL_TXDIVSEL_COMM_OUT

(1)

Loading...

Loading...