42 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 3: Simulation

R

Ports and Attributes

The GTP_DUAL primitive has attributes intended only for simulation. Table 3-1 lists the

simulation-only attributes of the GTP_DUAL tile. The names of these attributes start with

SIM_.

There are no simulation-only ports.

Description

The behavior of the GTP_DUAL tile is modeled using a SmartModel. The SmartModel

allows the design containing GTP_DUAL tiles to be simulated in the following design

phases:

• Register Transfer Level (RTL)/Pre-Synthesis Simulation

• Post-Synthesis Simulation/Pre-NGDBuild Simulation

• Post-NGDBuild/Pre-Map Simulation

• Post-Map/Partial Timing Simulation

• Post-Place and Route/Timing Simulation

Limitations

The analog nature of some blocks inside the GTP_DUAL tile generates some restrictions

when simulated using an HDL simulator. Receiver detection and OOB/beacon signaling

are analog features of the GTP_DUAL tile that can only be modeled in a limited way with

an HDL simulator. The shared PMA PLL is another analog block in the GTP_DUAL that is

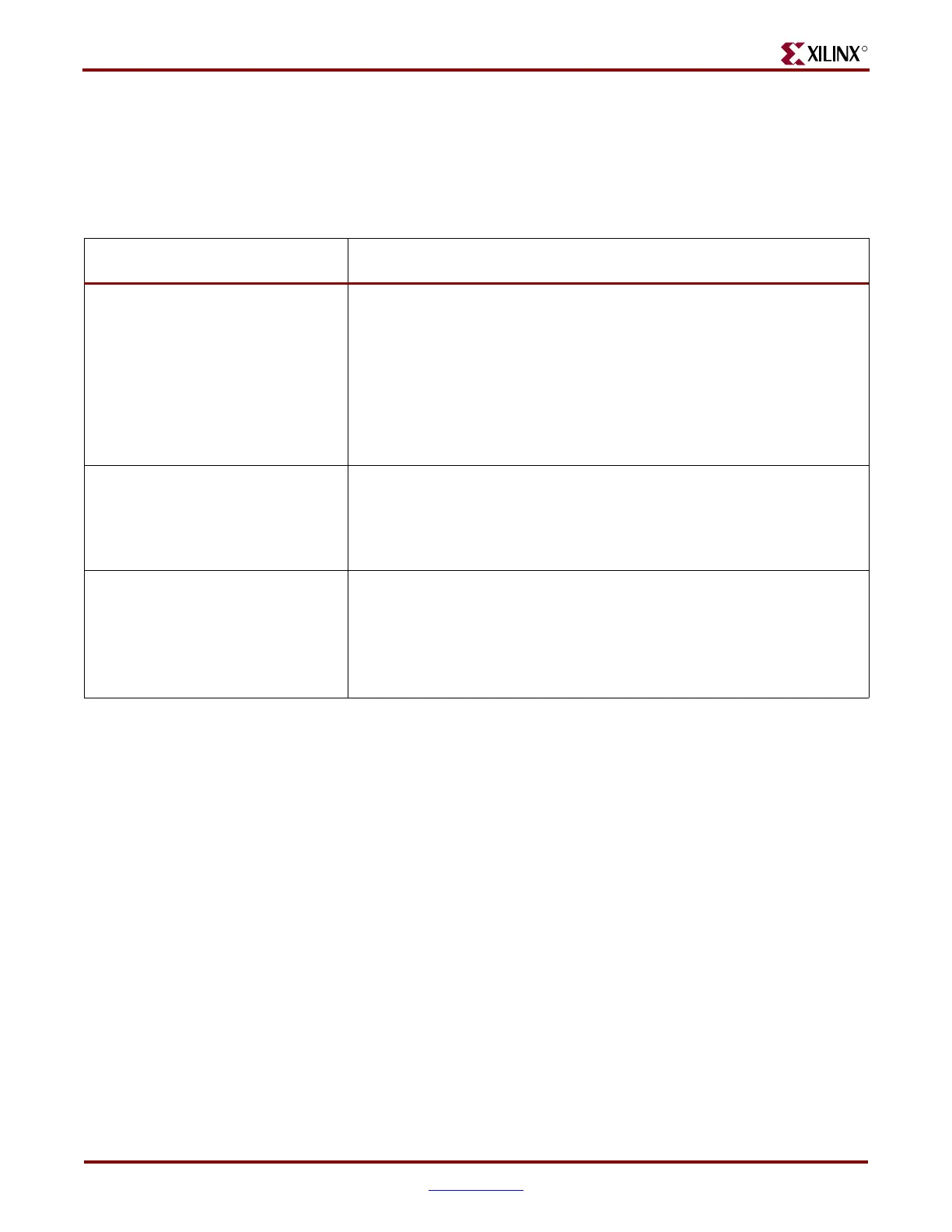

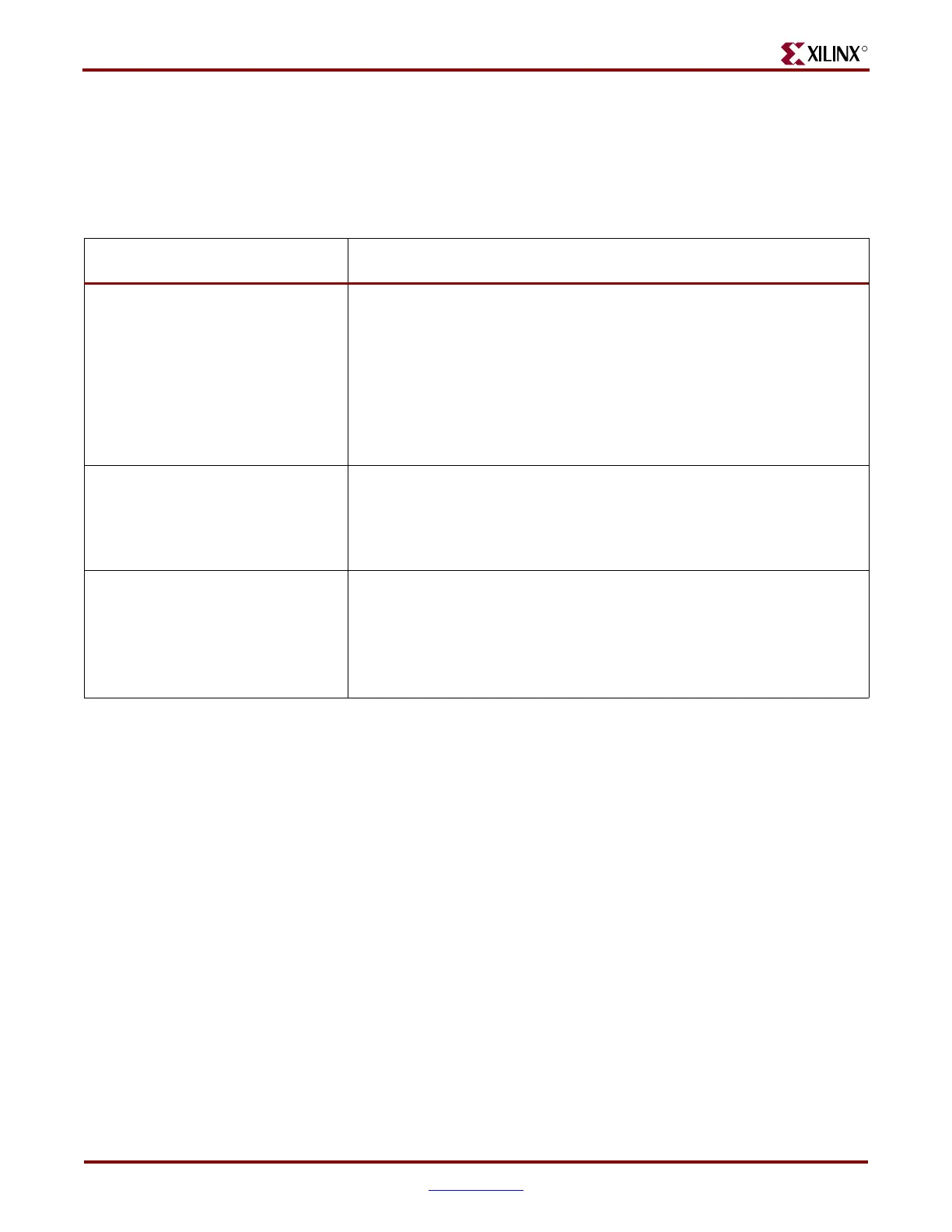

Table 3-1: GTP_DUAL Simulation-Only Attributes

Attribute Description

SIM_GTPRESET_SPEEDUP

This attribute shortens the time it takes to finish the GTPRESET sequence and

lock the shared PMA PLL during simulation.

TRUE: Shorten the GTPRESET cycle time (fast initialization is

approximately 300 ns). The value of SIM_PLL_PERDIV2 defines the PLL

frequency in this mode. Because SIM_PLL_PERDIV2 cannot be changed on

the fly during simulation, this mode cannot be used for multirate designs.

FALSE: The GTPRESET sequence is simulated with its original duration

(standard initialization is approximately 160 μs). This mode must be used

for multirate designs.

SIM_PLL_PERDIV2

This attribute specifies a 9-bit hex value equal to half the period of the PLL

clock frequency in picoseconds [ps]. For example, 400 ps (decimal) is equal to

0x190 (hexadecimal), which is the default value.

If SIM_PLL_PERDIV2 is not set correctly, poor locking behavior and incorrect

clock frequencies will occur in simulation.

SIM_RECEIVER_DETECT_PASS0

SIM_RECEIVER_DETECT_PASS1

This attribute is used to simulate the TXDETECTRX feature in each GTP

transceiver.

TRUE (default): Simulates an RX connection to the TX serial ports.

TXDETECTRX reports that an RX port is connected.

FALSE: Simulates a disconnected TX port. TXDETECTRX will report that

the RX port is not detected.

Loading...

Loading...