Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 95

UG196 (v1.3) May 25, 2007

FPGA TX Interface

R

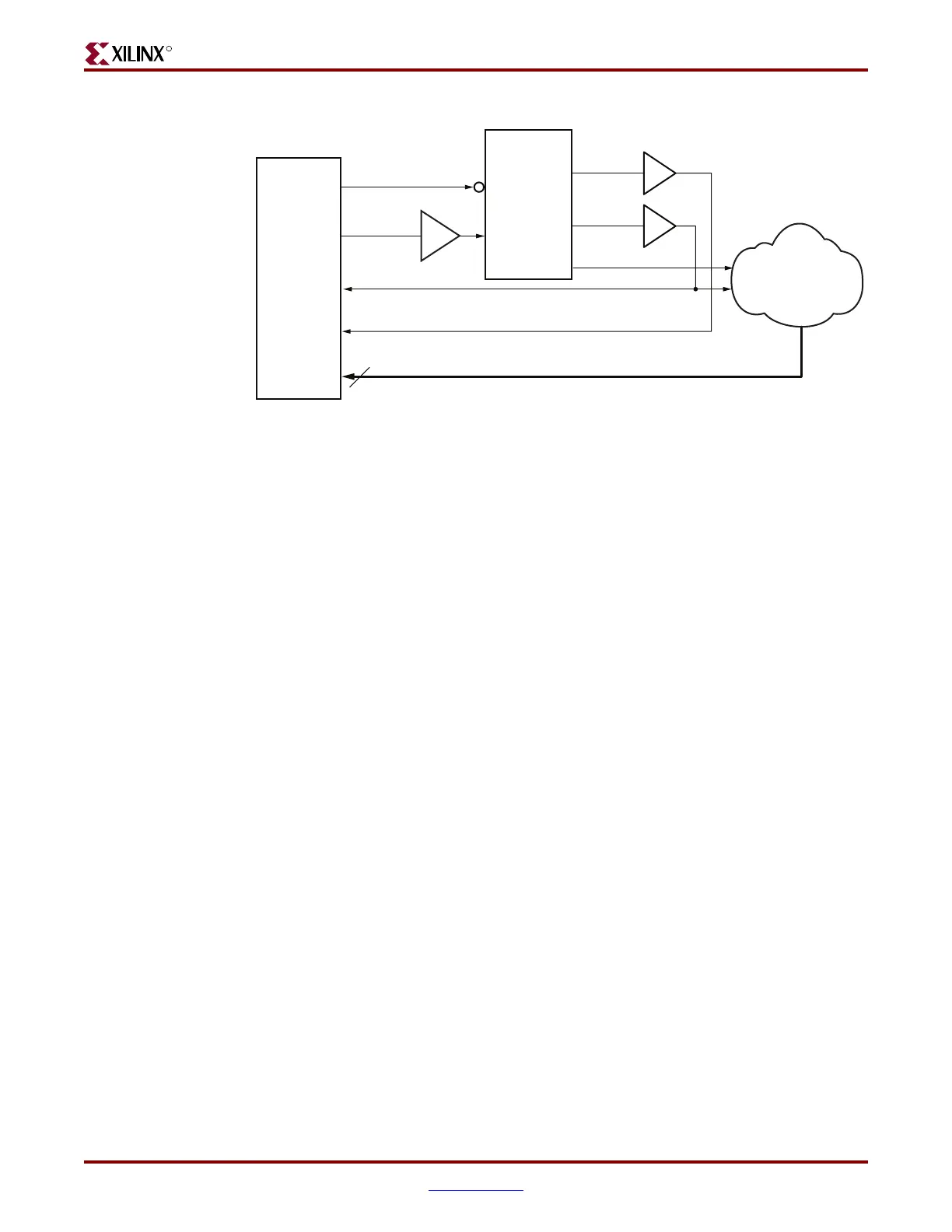

TXOUTCLK Driving Multiple Transceivers for a 2-Byte Datapath

Figure 6-7 shows TXOUTCLK driving multiple GTP user clocks. In this situation, the

frequency must be correct for all GTP transceivers, and they must share the same reference

clock. In Figure 6-7, because the top GTP transceiver uses a two-byte interface, it requires a

divided clock for TXUSRCLK2.

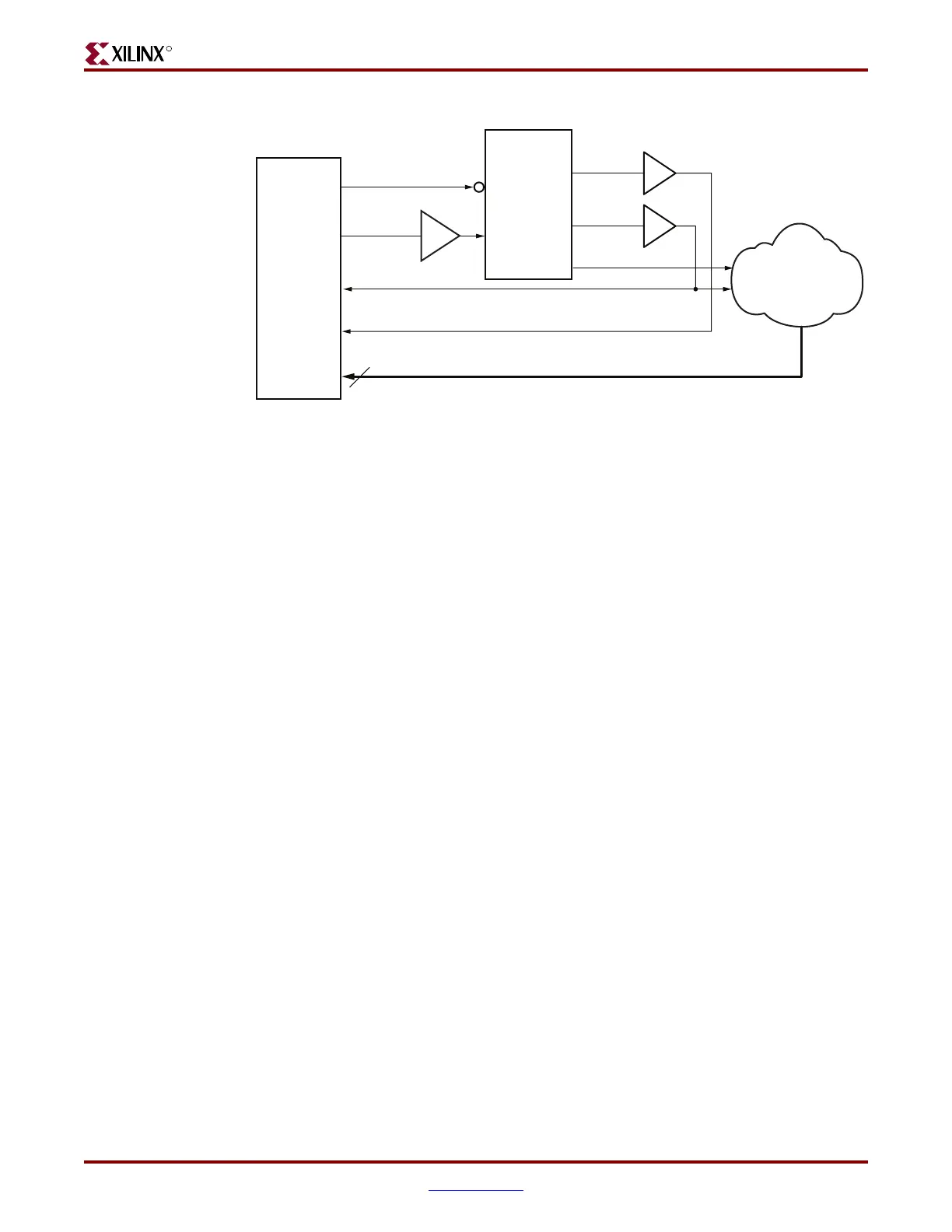

Figure 6-6: PLL Provides Clocks for a 2-Byte Datapath

GTP

Transceiver

PLL_BASE

CLKIN

RST

CLKOUT0

PLLLKDET

TXOUTCLK

TXUSRCLK2

TXUSRCLK

TXDATA (16 or 20 bits)

CLKOUT1

LOCKED

Design in

FPGA

UG196_c6_06_032907

BUFG

Loading...

Loading...