Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 19

UG196 (v1.3) May 25, 2007

R

Chapter 1

Introduction to the RocketIO GTP

Transceiver

Overview

The RocketIO GTP transceiver is a power-efficient transceiver for Virtex™-5 FPGAs. The

GTP transceiver is highly configurable and tightly integrated with the programmable logic

resources of the FPGA. It provides the following features to support a wide variety of

applications:

• Current Mode Logic (CML) serial drivers/buffers with configurable termination,

voltage swing, and coupling

• Programmable TX pre-emphasis and RX equalization for optimized signal integrity

• Line rates from 100 Mb/s to 3.2 Gb/s, with optional 5x digital oversampling required

for rates between 100 Mb/s and 500 Mb/s

• Optional built-in PCS features, such as 8B/10B encoding, comma alignment, channel

bonding, and clock correction

• Fixed latency modes for minimized, deterministic datapath latency

• Out of band signaling, including COM signal support for PCI Express and SATA

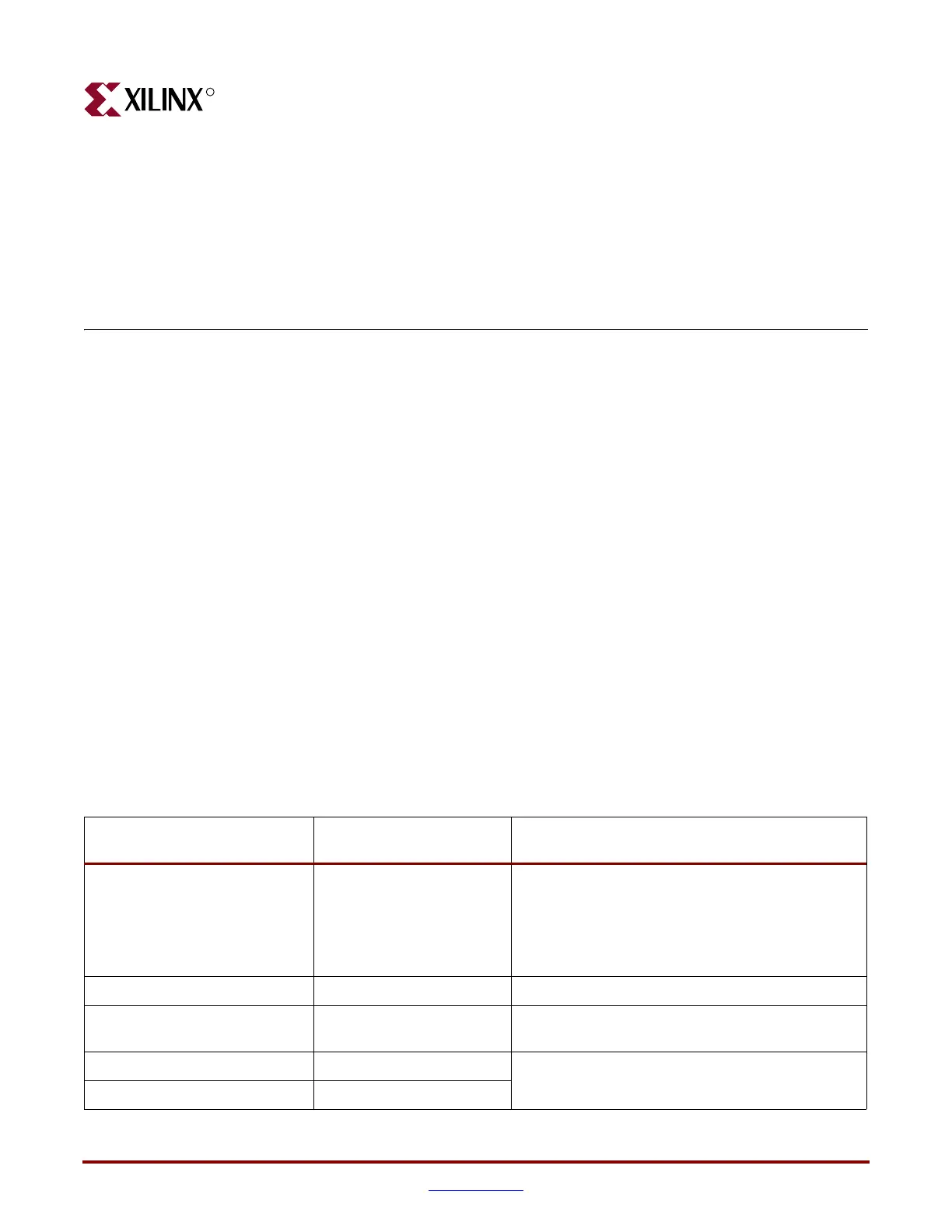

Table 1-1 lists some of the standard protocols designers can implement using the GTP

transceiver. The Xilinx CORE Generator™ tool includes a Wizard to automatically

configure GTP transceivers to support one of these protocols or perform custom

configuration (see Chapter 2, “RocketIO GTP Transceiver Wizard”).

Table 1-1: List of Standards Supported by the GTP_DUAL Tile

Protocols Supported

Protocol Data Rates

Supported

Miscellaneous Features

PCI Express Rev 1.0a

PCI Express Rev 1.1

2.5 Gb/s • TX receive detect

• Loss of Signal (LOS)/Idle state detect

• Low power states

• Out Of Band Beacon

• Ground Referenced termination

XAUI 802.3ae D5p0 3.125 Gb/s • LOS

OC-12/48 622.08/2488.32 Mb/s • Allow bypassing FIFOs for synchronous

operation (not jitter transfer compliant)

FC-1 Rev 4.0 1.0625 Gb/s • Rate negotiation (allows operating the TX and RX

at different speeds)

FC-2 Rev 4.0 2.125 Gb/s

Loading...

Loading...