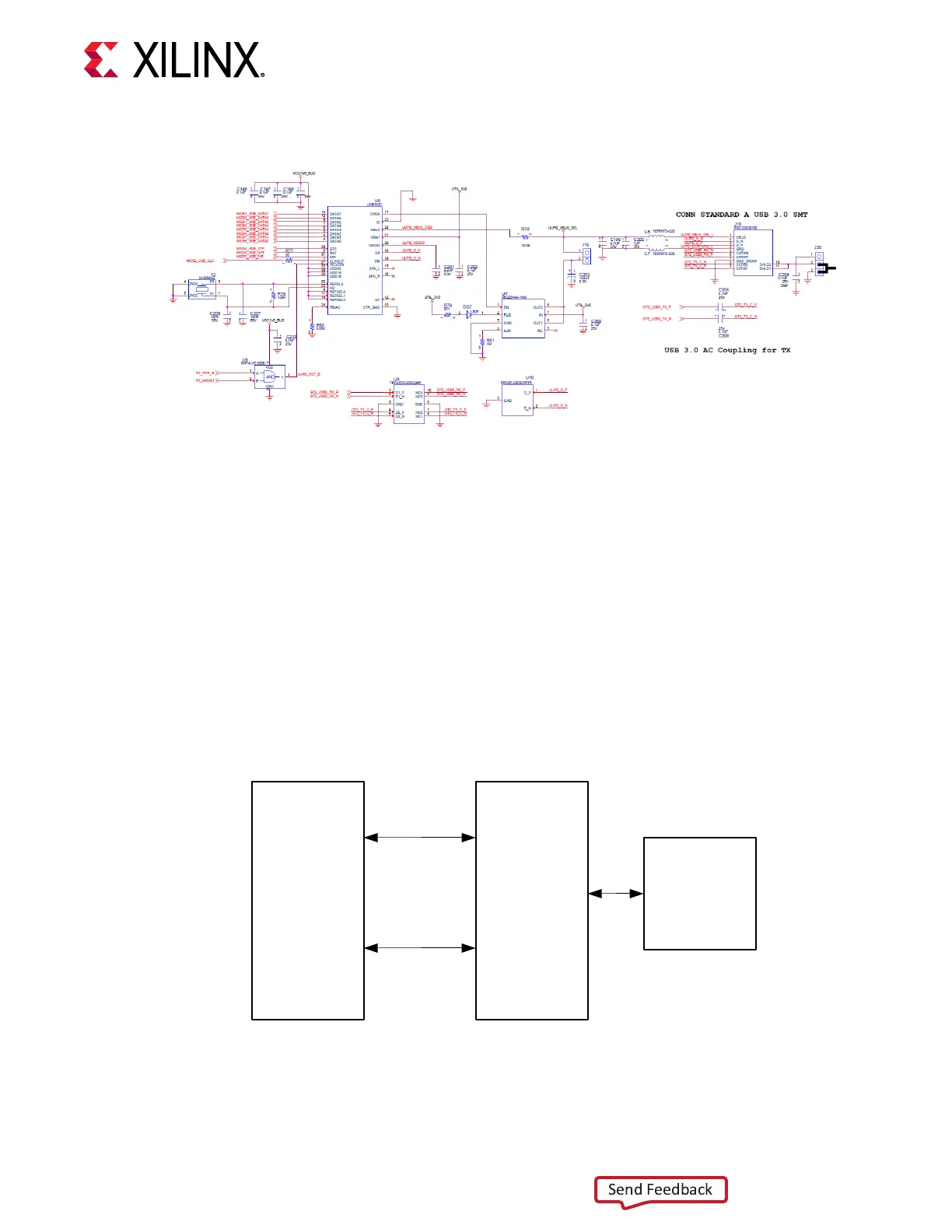

Figure 12: USB3320 ULPI USB 2.0 Transceiver Circuit

The detailed RFSoC connecons for the feature described in this secon are documented in the

ZCU216 board XDC le, referenced in Appendix B: Xilinx Design Constraints.

GEM3 Ethernet (MIO 64-77)

[Figure 2, callout 16]

The PS-side Gigabit Ethernet MAC (GEM) implements a 10/100/1000 Mb/s Ethernet interface,

shown in the following gure, which connects to a TI DP83867IRPAP Ethernet RGMII PHY

before being routed to an RJ45 Ethernet connector. The RGMII Ethernet PHY is boot strapped to

PHY address 5'b01100 (0x0C) and Auto Negoaon set to Enable. Communicaon with the

device is covered in the TI DP83867 RGMII PHY data sheet on the Texas Instruments website.

Figure 13: Ethernet Block Diagram

TI

DP83867IR

GEM

MIO

RGMII

MDIO

RJ45 and

Magnetics

X23310-093019

Chapter 3: Board Component Descriptions

UG1390 (v1.1) July 10, 2020 www.xilinx.com

ZCU216 Board User Guide 41

Loading...

Loading...