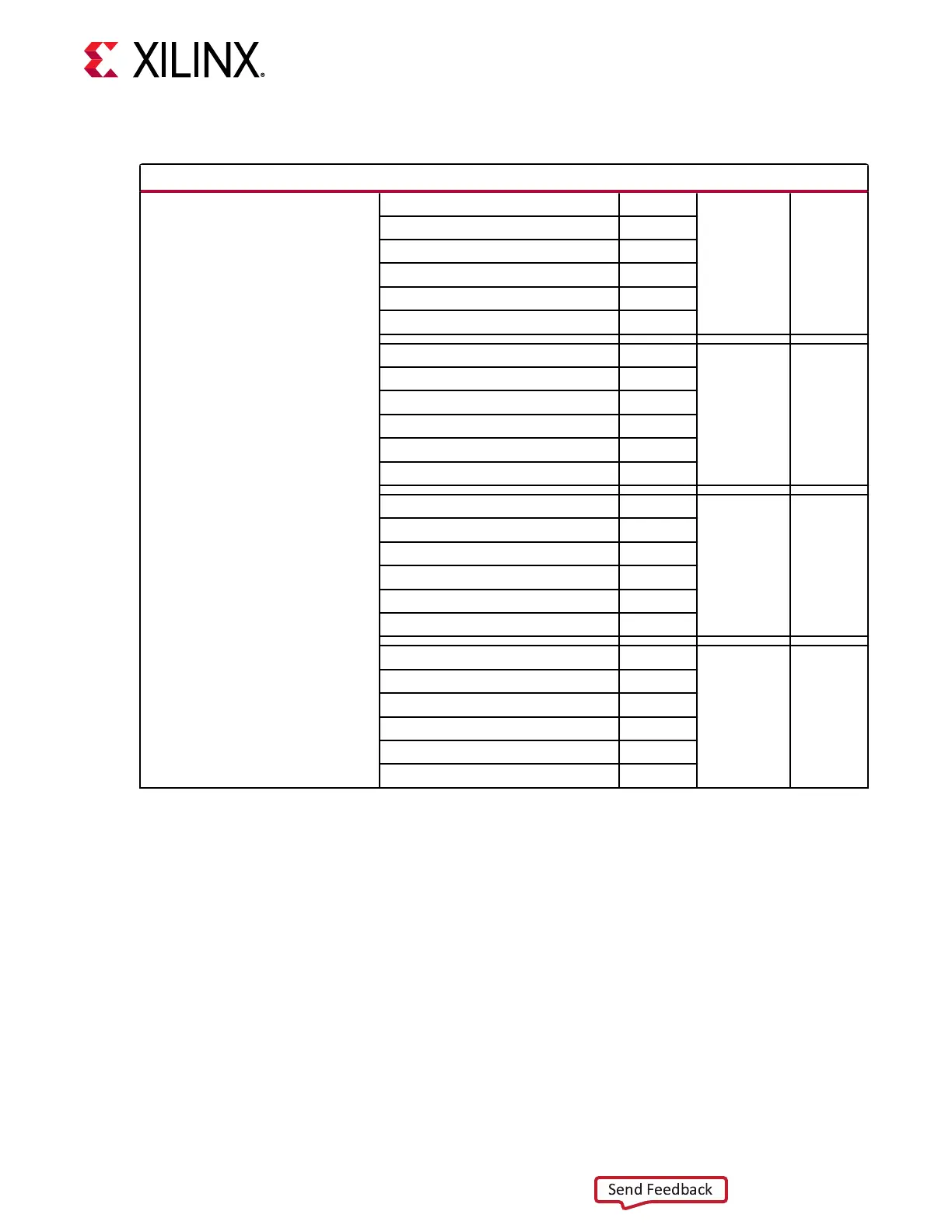

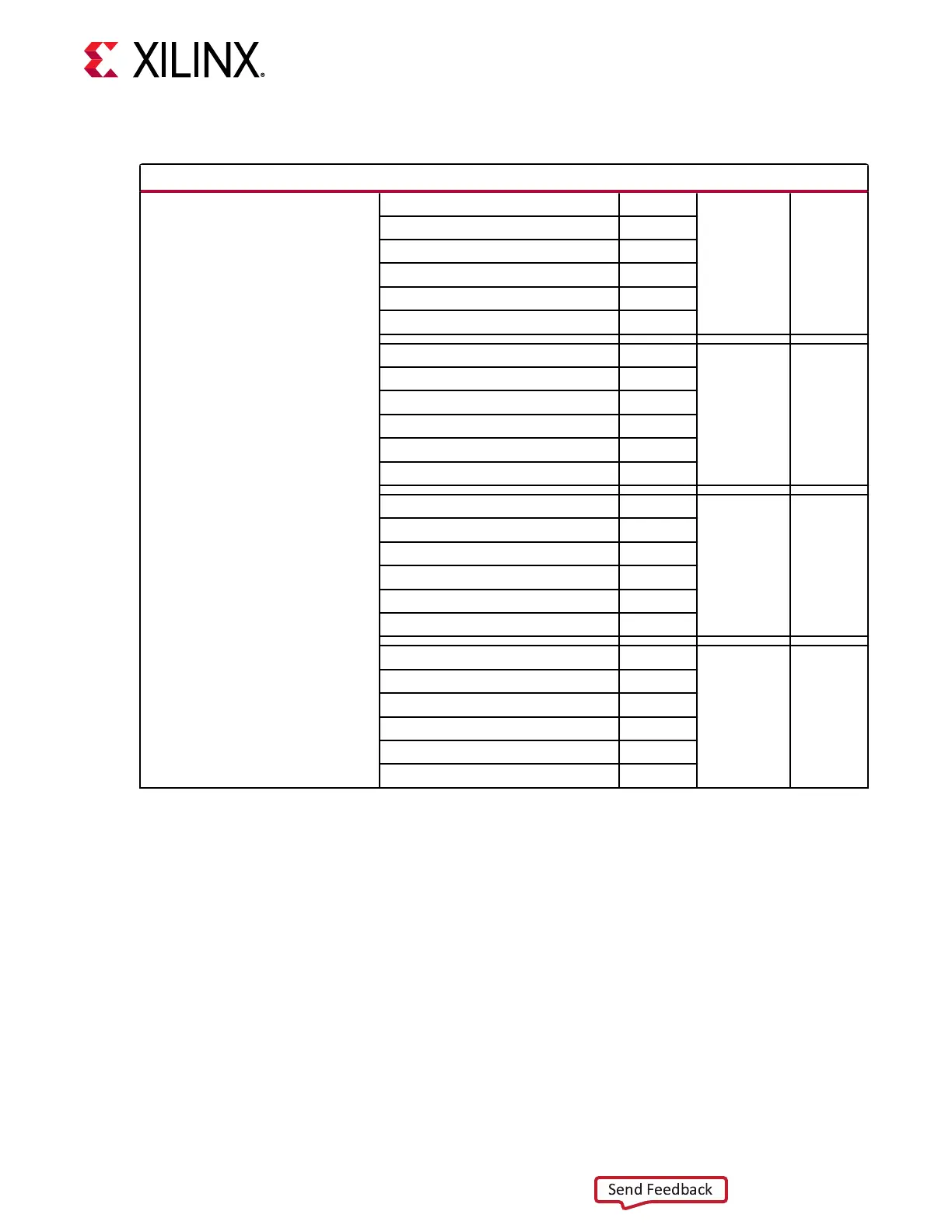

Table 21: ZCU216 ZU49DR GTY Mapping

ZCU216 ZU49DR-FFVF1760 GTY Mapping

ZU49DR-FFVF1760

8A34001 CLK1_IN - Q1_OUT ch3

GTY Quad 128 PCIe4

NO CONNECT

ch2

zSFP1 ch1

zSFP0 ch0

8A34001 Q11_OUT refclk1

8A34001 CLK5_IN refclk0

CoreHC2 1x8 Connector ch3

GTY Quad 129 CMAC

NO CONNECT

ch2

zSFP3 ch1

zSFP2 ch0

8A34001 Q7_OUT refclk1

8A34001 CLK6_IN refclk0

FMC DP3 ch3

GTY Quad 130 ILKN

FMC DP2

ch2

FMC DP1 ch1

FMC DP0 ch0

USER_SMA_MGT_CLOCK refclk1

FMC GBTCLK0 M2C refclk0

FMC DP7 ch3

GTY Quad 131 PCIe4

FMC DP6

ch2

FMC DP5 ch1

FMC DP4 ch0

USER_MGT_SI570_CLOCK refclk1

FMC GBTCLK1 M2C refclk0

FMCP HSPC

Eight MGTs are provided by PL-side MGT banks 130 and 131. Available MGT reference clocks

include the FMC dened GBT clocks 0 and 1, a programmable SI570 clock and a dierenal SMA

clock.

zSFP+

Four MGTs are provided by PL-side MGT banks 128 and 129 for the quad (2x2 connector) zSFP+

interface. Available GTY reference clocks include two sets of clocks to/from IDT 8A34001 U409.

Each zSFP+ connector provides an I2C based control interface. This I2C interface is accessible for

each individual zSFP+ module through the I2C mulplexer topology on the ZCU216.

Chapter 3: Board Component Descriptions

UG1390 (v1.1) July 10, 2020 www.xilinx.com

ZCU216 Board User Guide 55

Loading...

Loading...