566 Chapter11

Synthesizer Section

Unlocked Fractional N PLL

9. Divider and integrator troubleshooting: Measure the frequency of

the pulses at TP6 in block AO. Look up the expected problem area in

Table 11-11 on page 566 and go to the appropriate troubleshooting

steps.

10.Divider troubleshooting:

a. Check the frequency at A14TP2. It should be equal to the

frequency at A14TP1 divided by two.

b. The signal at A14TP3 should be greater than −14 dBm.

c. Use an analog oscilloscope to view the signal at A14TP5. Adjust

the scope triggering to view the divide-by-16 signal. The

frequency at this point will be varying as the prescaler changes

its divide number to either 16, 17, 20, or 21. The prescaler uses 16

as the divide number most frequently. The frequency displayed on

the oscilloscope should equal the frequency from TP2 divided by

16.

d. Use an oscilloscope to view the signal at pin 8 of U112. Its

average frequency should be given by:

f = f(A14TP5) × 80 MHz/RAW OSC FREQ

where: f(A14TP5) is the frequency measured at TP5, and RAW

OSC FREQ comes from step 4 (A14TP1).

If the frequency is in error, the fractional divider, block AS, is not

functioning. Check that FRAC N RUN on U113 pin 39 is high.

e. Use an oscilloscope to verify that the signals at N_in (U112 pin 8)

and N_out (TP6) are identical except for a sub-microsecond delay.

Detector and integrator troubleshooting: Check the phase detector

output on TP11 in block AO. If F_ref is higher in frequency than TP6

(reclocked VCO/N), then the average voltage at TP11 should be

positive by 0.05 V to 10 V. If F_ref is lower, TP11 should be −0.05 V to

−10 V.

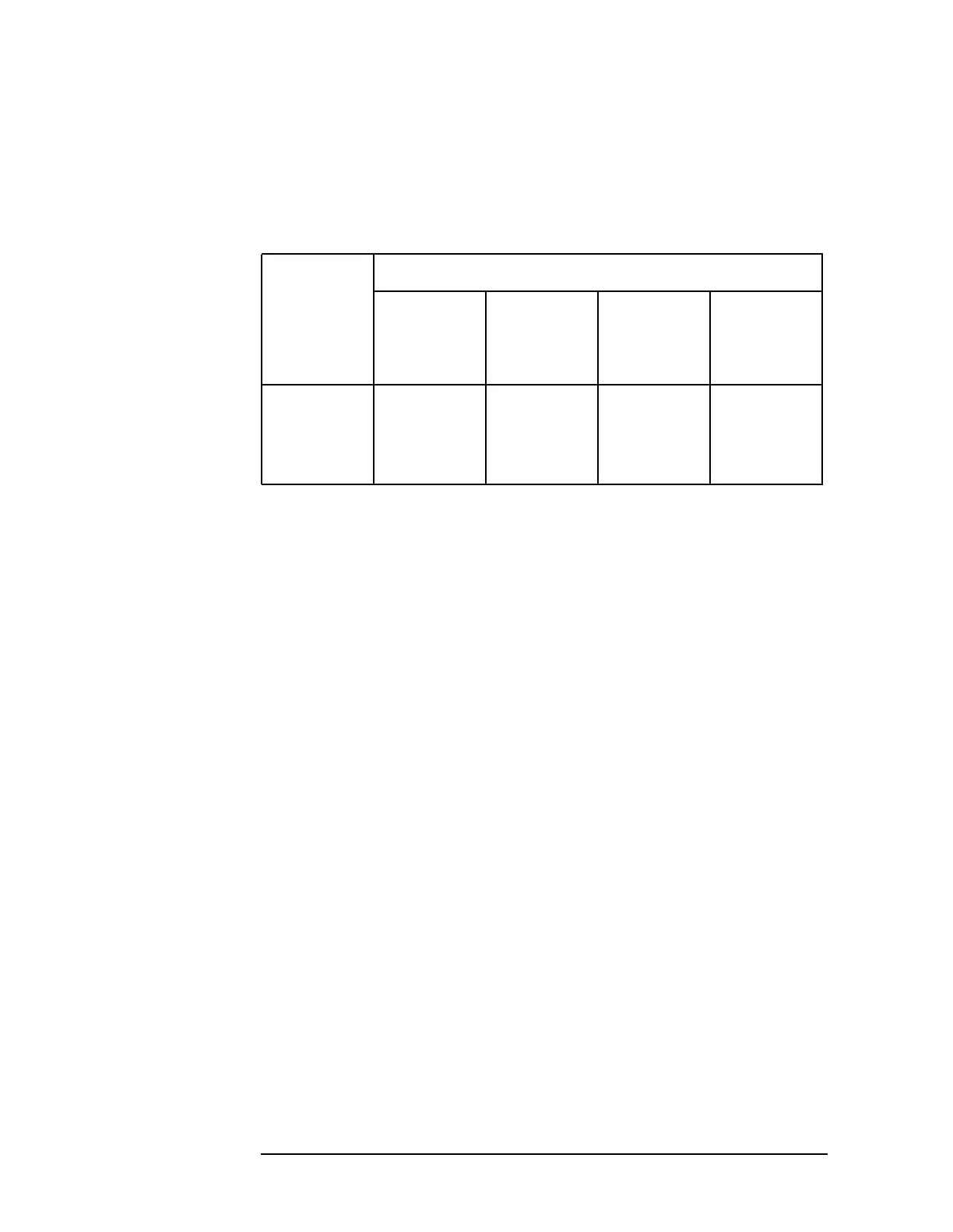

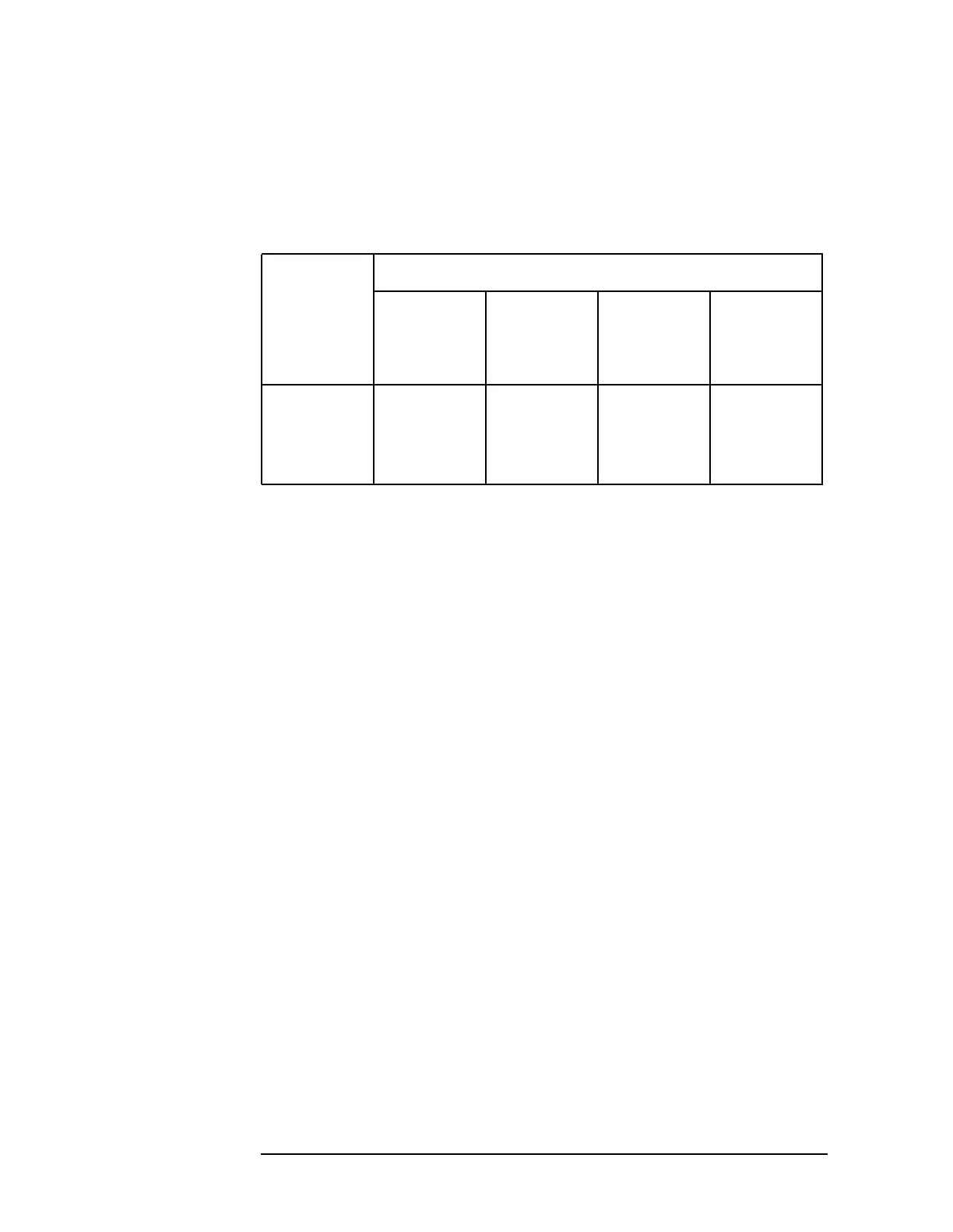

Table 11-11 Divider and Integrator Troubleshooting

Measured

VCO

Frequency

Relative to

Expected

Value

TP6 Frequency

zero <2.5 MHz 2.5 MHz >2.5 MHz

Measured >

expected

Dividers Dividers Dividers Detector or

integrator

Measured <

expected

Both Detector or

integrator

Dividers Dividers

Loading...

Loading...