MSC Q7-BT MSC_Q7-BT_User_Manual.pdf 37 / 113

4.7 eDP

The eDP signals shared with LVDS channel A.

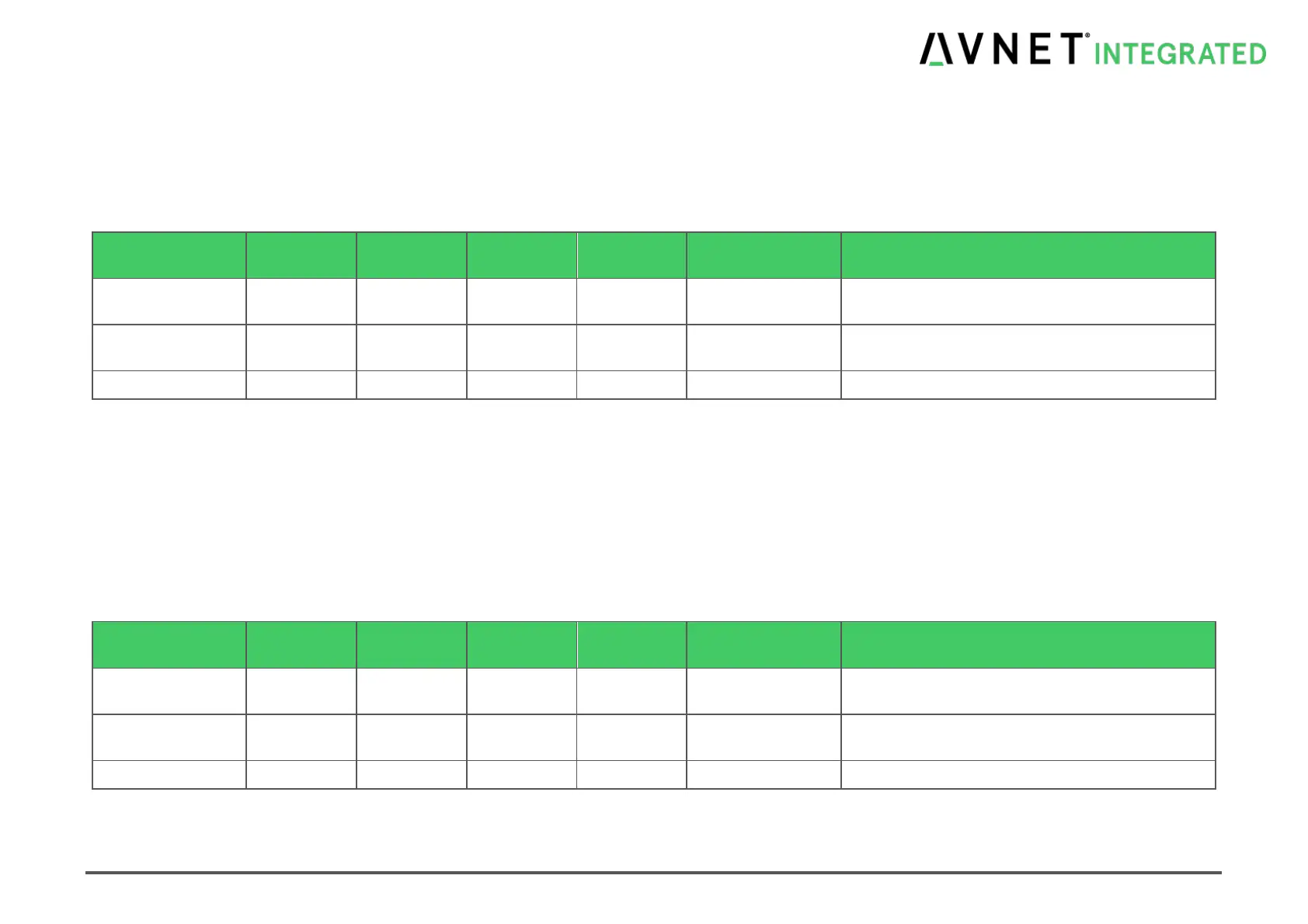

Table 4-8 eDP Signal Description

eDP0_LANE[0:3]+

eDP0_LANE[0:3]-

Differential signal pair for DP lane [0:3]

AUX+ PD 100k

AUX- PU 100k 3.3V

Differential signal pair for eDP0 AUX channel

4.8 Dual Mode Display Port (DP++)

The SoC is able to detect what kind of display is connected to the DP++ interface and switches the transmitted data format automatically between

packet organized DP format and TMDS based format for HDMI/DVI. Physically the interface is an AC coupled signal as used in DP implementations.

Therefore the baseboard requires some form of level shifting hardware to connect these signals to an HDMI/DVI connector.

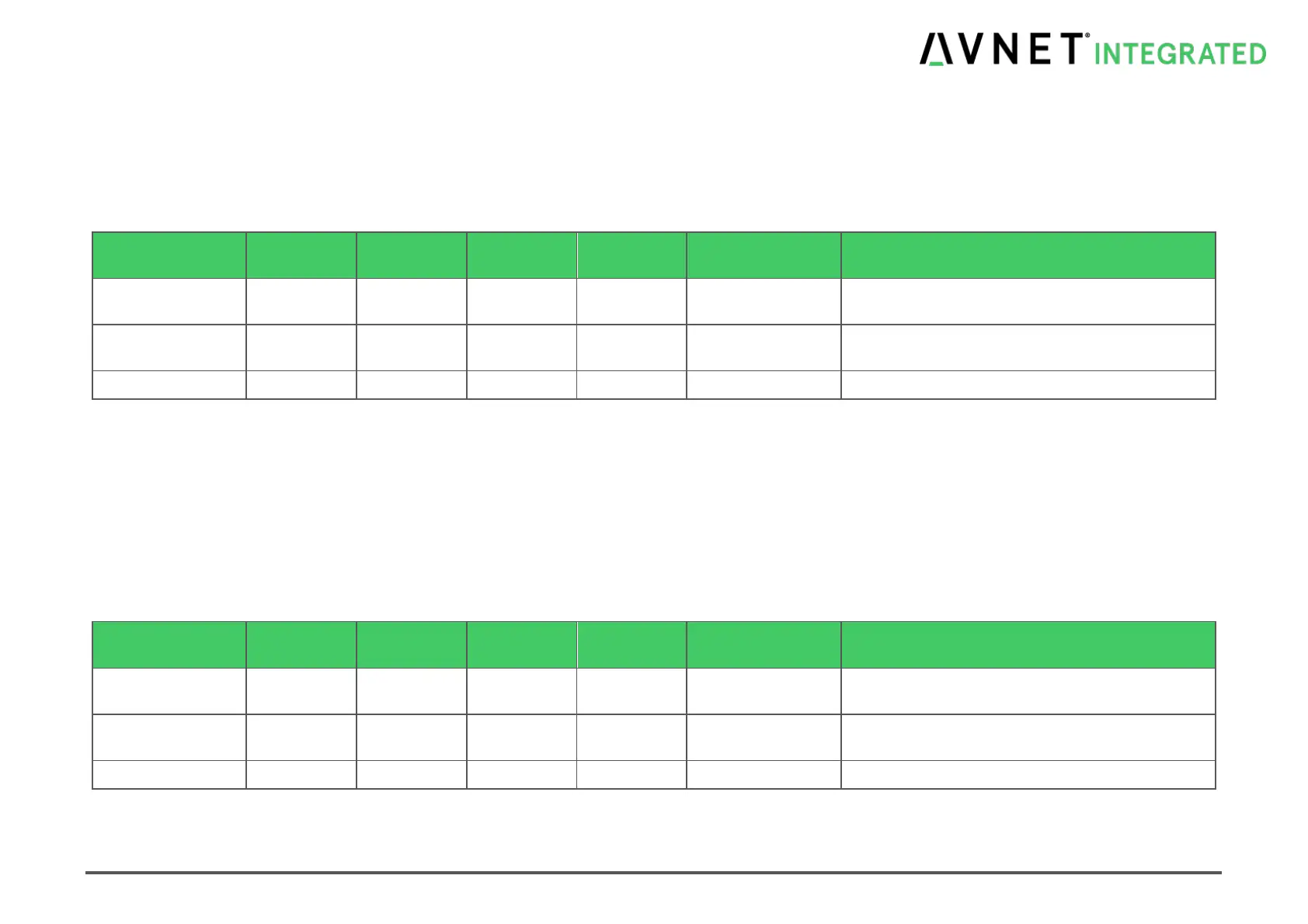

Table 4-9 Display Port Signal Description

DP_LANE[0..3]+

DP_LANE[0..3]-

Differential signal pair for DP lane [0:3]

AUX+ PD 100k

AUX- PU 100k 3.3V

Differential signal pair for eDP AUX channel

Loading...

Loading...