MSC Q7-BT MSC_Q7-BT_User_Manual.pdf 35 / 113

4.6 LVDS

The LVDS channel A signals are shared with the eDP signals.

LVDS-Controller: Analogix ANX1122

Supported LVDS panels:

Supported resolutions up to WQXGA (2560x1600, 60Hz, 24bpp) with pixel clock frequency up to 270MHz

18bpp and 24bpp

Single and Dual Channels.

For ANX1122, pixel rates up to 270 MHz are supported for the dual channel LVDS outputs.

For the single channel LVDS output, the pixel rate can be up to 135 MHz.

Minimum pixel clock is 10MHz

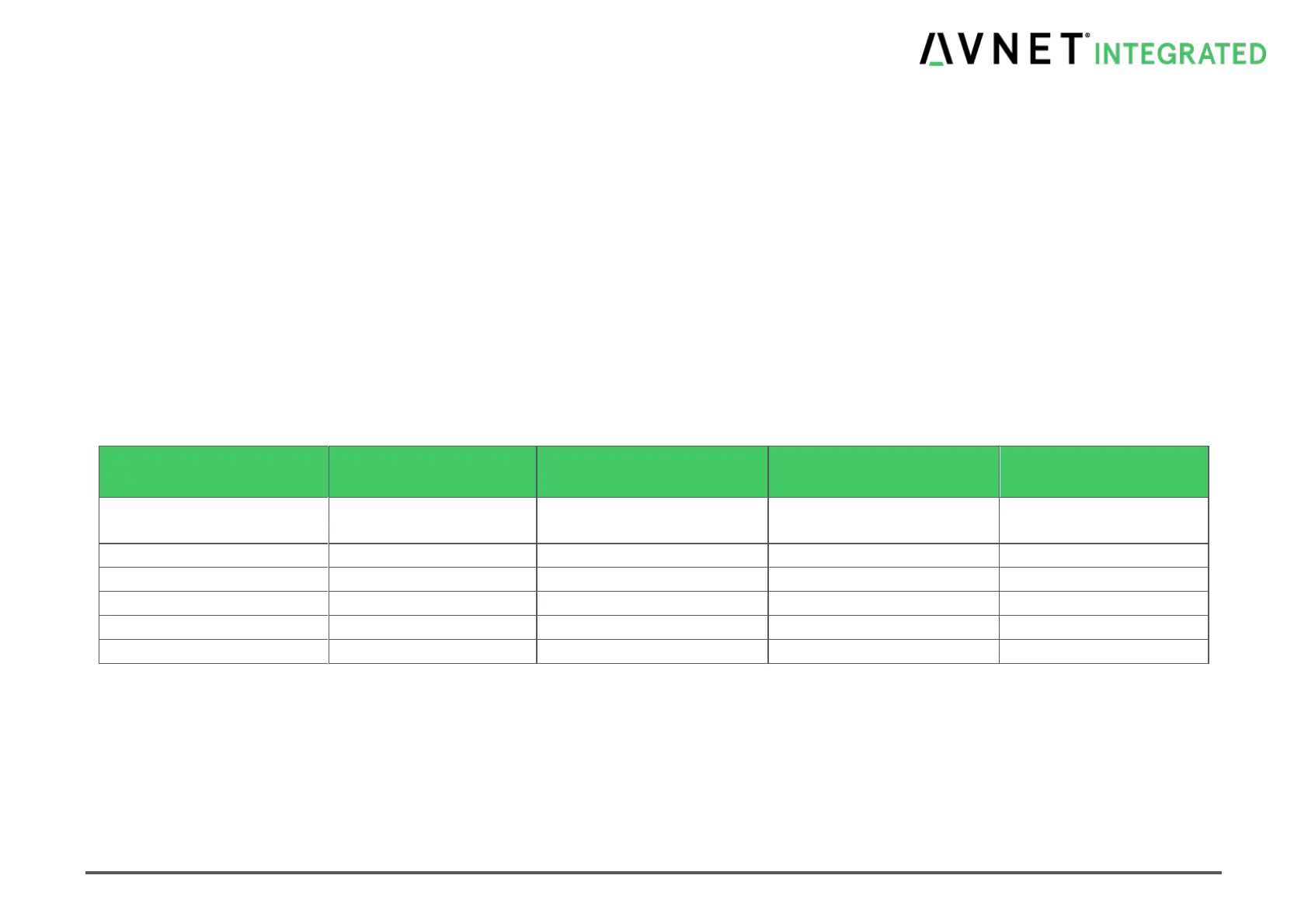

Table 4-6 ANX1122 Supported Video Formats

Video Timing

(Hor * Ver @ Frame Rate)

Pixel Clock Frequency (MHz)

18 Bits per Pixel

Pixel Clock Frequency (MHz)

24 Bits per Pixel

Stream Bit Rate (Gbps)

1600x1200@60Hz, CVT

(reduced blanking)

Loading...

Loading...