CHAMP-AV8 (VPX6-462) HARDWARE USER’S MANUAL CURTISS-WRIGHT

A-18 PROPRIETARY 826448 VERSION 5 MARCH 2015

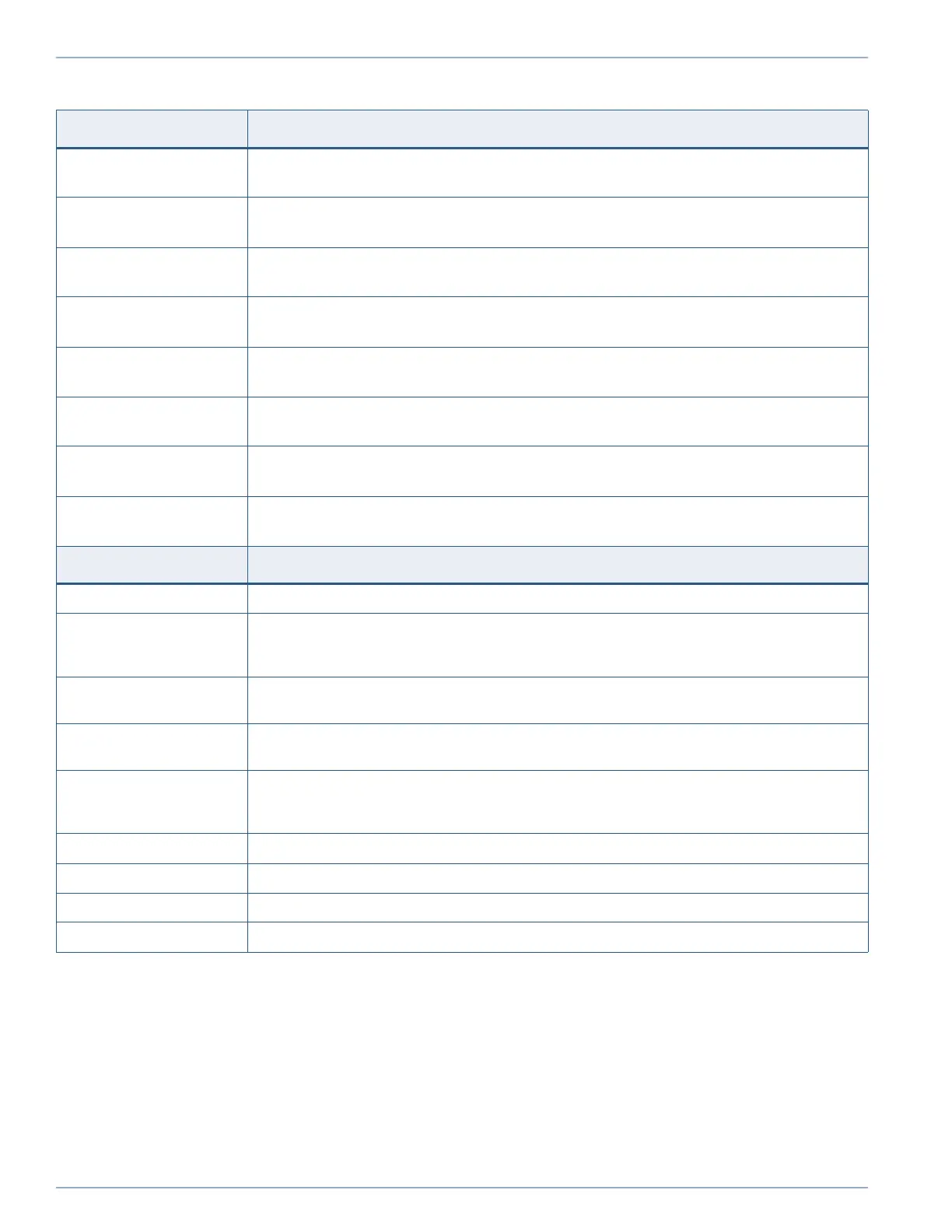

Table A.7: P1 SRIO Fabric Connector Signal Definitions

CHAMP-AV8 Signal Description

PA_TX_P[0:3]

PA_TX_N[0:3]

SRIO Port A Transmit Data Pairs - 4x-LP Transmit Pairs

P1-DPX+/- (X =1,3,5,7)

PA_RX_P[0:3]

PA_RX_N[0:3]

SRIO Port A Receive Data Pairs - 4x-LP Receive Pairs

P1-DPX+/- (X =0,2,4,6)

PB_TX_P[0:3]

PB_TX_N[0:3]

SRIO Port B Transmit Data Pairs - 4x-LP Transmit Pairs

P1-DPX+/- (X =9,11,13,15)

PB_RX_P[0:3]

PB_RX_N[0:3]

SRIO Port B Receive Data Pairs - 4x-LP Receive Pairs

P1-DPX+/- (X =8,10,12,14)

PC_TX_P[0:3]

PC_TX_N[0:3]

SRIO Port C Transmit Data Pairs - 4x-LP Transmit Pairs

P1-DPX+/- (X =17,19,21,23)

PC_RX_P[0:3]

PC_RX_N[0:3]

SRIO Port C Receive Data Pairs - 4x-LP Receive Pairs

P1-DPX+/- (X =16,18,20,22)

PD_TX_P[0:3]

PD_TX_N[0:3]

SRIO Port D Transmit Data Pairs - 4x-LP Transmit Pairs

P1-DPX+/- (X =25,27,29,31)

PD_RX_P[0:3]

PD_RX_N[0:3]

SRIO Port D Receive Data Pairs - 4x-LP Receive Pairs

P1-DPX+/- (X =24,26,28,30)

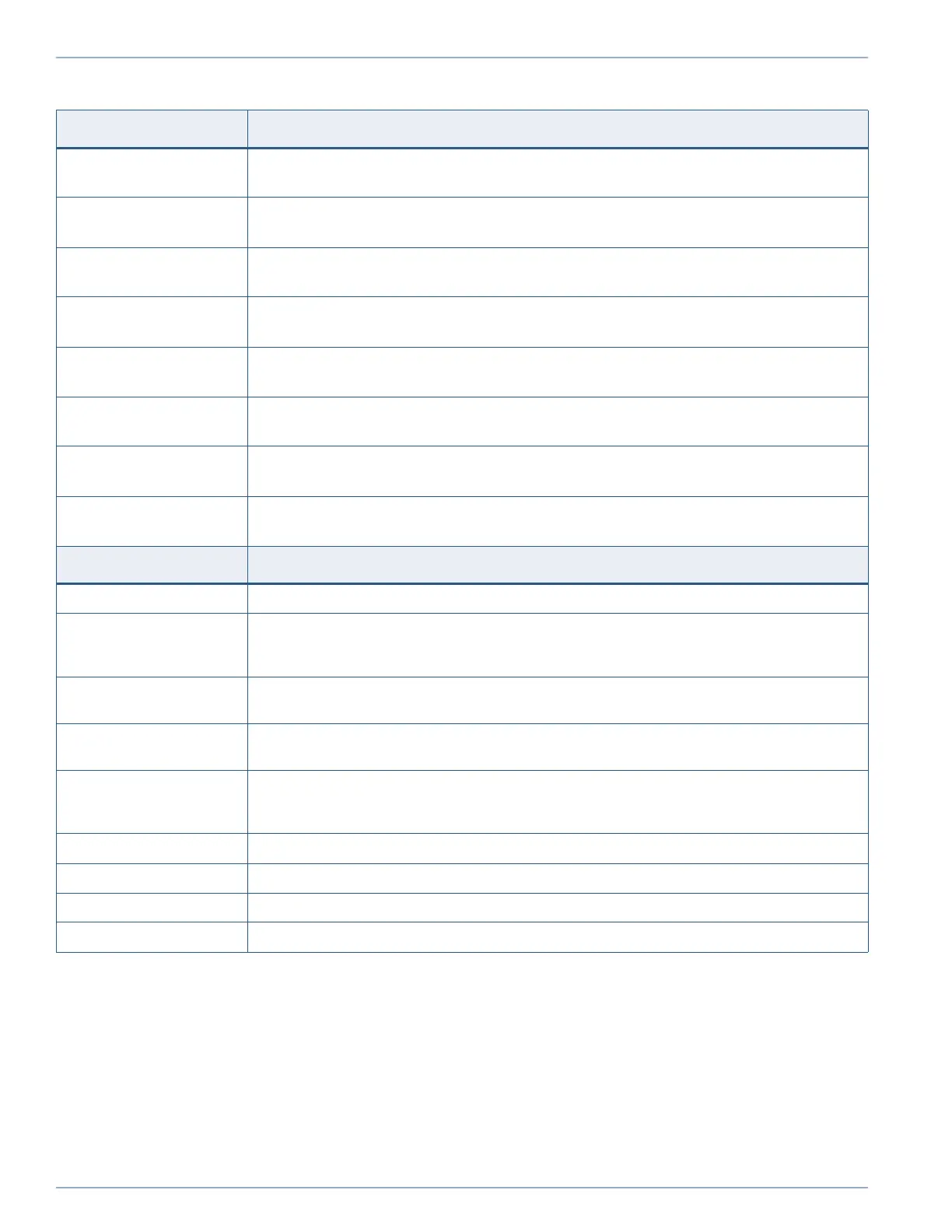

CHAMP-AV8 Signal Description

BP_GDISCRETE1 Used for MBSC Sync Signal.

SYS_CON_L SYSCON_L - VITA 46.0 signal that indicates which slot is the system controller. Open collector

driven by backplane; pull-up to 3.3V is implemented on board. When driven low by the backplane,

the CHAMP-AV8 will become the source of the SYSRST_L and REF_CLK_P/N signals.

CF_ALT_BOOT_L Alternate Boot Enable Input - Maps the boot chip select on all of the processors to the Permanent

Alternate Boot Site (PABS) PROM; pull-up to 3.3V is implemented on board.

CARD_FAIL_L Card Fail Output - Active low signal that indicates a card failure. This signal uses 3.3V LVCMOS

signaling.

MASKABLE

RESET_L

Pushbutton Reset input - Active low, open collector signal that initiates a board reset; pulled up to

3.3V on board. This signal is also available on the front panel J1 connector pin 19 (air-cooled vari-

ants).

VBAT VITA 46.0 VBAT Power

GND Ground signals as defined in VITA 46.0.

NC_RFU Reserved IO Signal - Reserved by Curtiss-Wright

NC_IO_RSRV Reserved IO Signal - Reserved by Curtiss-Wright

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...