CURTISS-WRIGHT 1

826448 VERSION 5 MARCH 2015 PROPRIETARY A-27

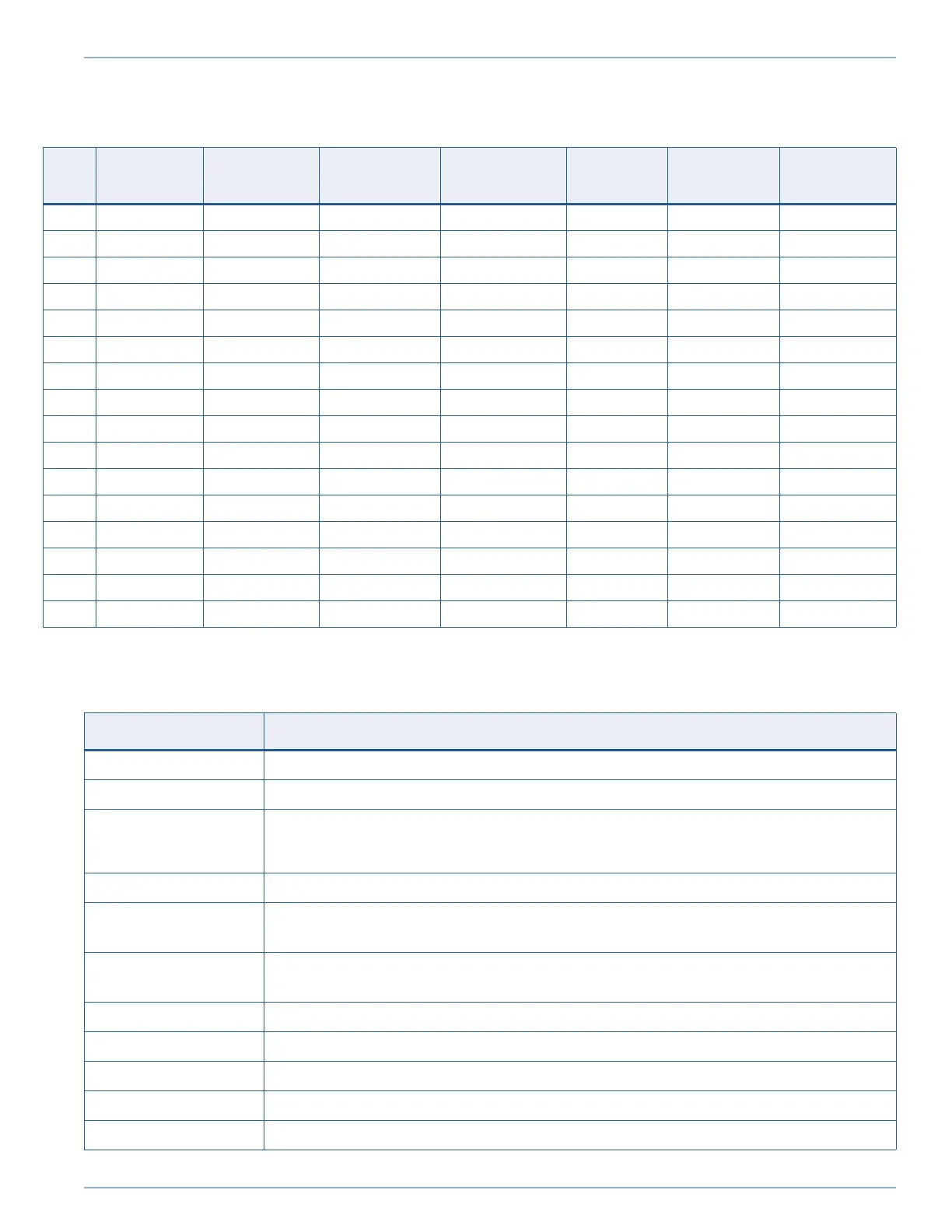

Table A.15: P4 Basecard I/O Connector Pin Assignments

Wafer

No.

Row G

Signal

Row F

Signal

Row E

Signal

Row D

Signal

Row C

Signal

Row B

Signal

Row A

Signal

1 BP_PABS_A_CS0_L GND JTSEL_L JPROC2 GND JPROC1 JPROC0

2 GND IPMI_SERIAL_OUT PMBUS_SDA GND PMI_TDI PMI_TDO GND

3 BP_PABS_A_CLK GND PMBUS_SCL JPROC3 GND PMI_TCK PMI_TMS

4 GND IPMI_SERIAL_IN CF_NAND_WR_DIS_L GND BP_PORT80_EN_L PMI_JTSEL_L GND

5 BP_PABS_A_SO GND CF_FLASH_WR_DIS_L CF_NVRAM_WR_DIS_L GND CF_PABS_WR_EN_L CF_PROM_WR_EN_L

6 GND CF_SOFT_JUMP_L_1 CF_SOFT_JUMP_L_0 GND CF_WD_DIS_L RS232_A0_RX GND

7 BP_PABS_A_SI GND RS422_RXA2_N RS422_RXA2_P GND RS422_TXA2_N RS422_TXA2_P

8 GND RS422_RXB2_N RS422_RXB2_P GND RS422_TXB2_N RS422_TXB2_P GND

9 BP_PABS_B_CS0_L GND RS232_A1_TX RS232_A1_RX GND RS232_A0_TX PMI_TRST_L

10 GND RS232_B0_TX RS232_B0_RX GND RS232_B1_TX RS232_B1_RX GND

11 BP_PABS_B_CLK GND UTP_B_TX_N UTP_B_TX_P GND UTP_B_RX_N UTP_B_RX_P

12 GND UTP_A_TX_N UTP_A_TX_P GND UTP_A_RX_N UTP_A_RX_P GND

13 BP_PABS_B_S0 GND ETH_A_TRX1_N ETH_A_TRX1_P GND ETH_A_TRX0_N ETH_A_TRX0_P

14 GND ETH_A_TRX3_N ETH_A_TRX3_P GND ETH_A_TRX2_N ETH_A_TRX2_P GND

15 BP_PABS_B_SI GND ETH_B_TRX1_N ETH_B_TRX1_P GND ETH_B_TRX0_N ETH_B_TRX0_P

16 GND ETH_B_TRX3_N ETH_B_TRX3_P GND ETH_B_TRX2_N ETH_B_TRX2_P GND

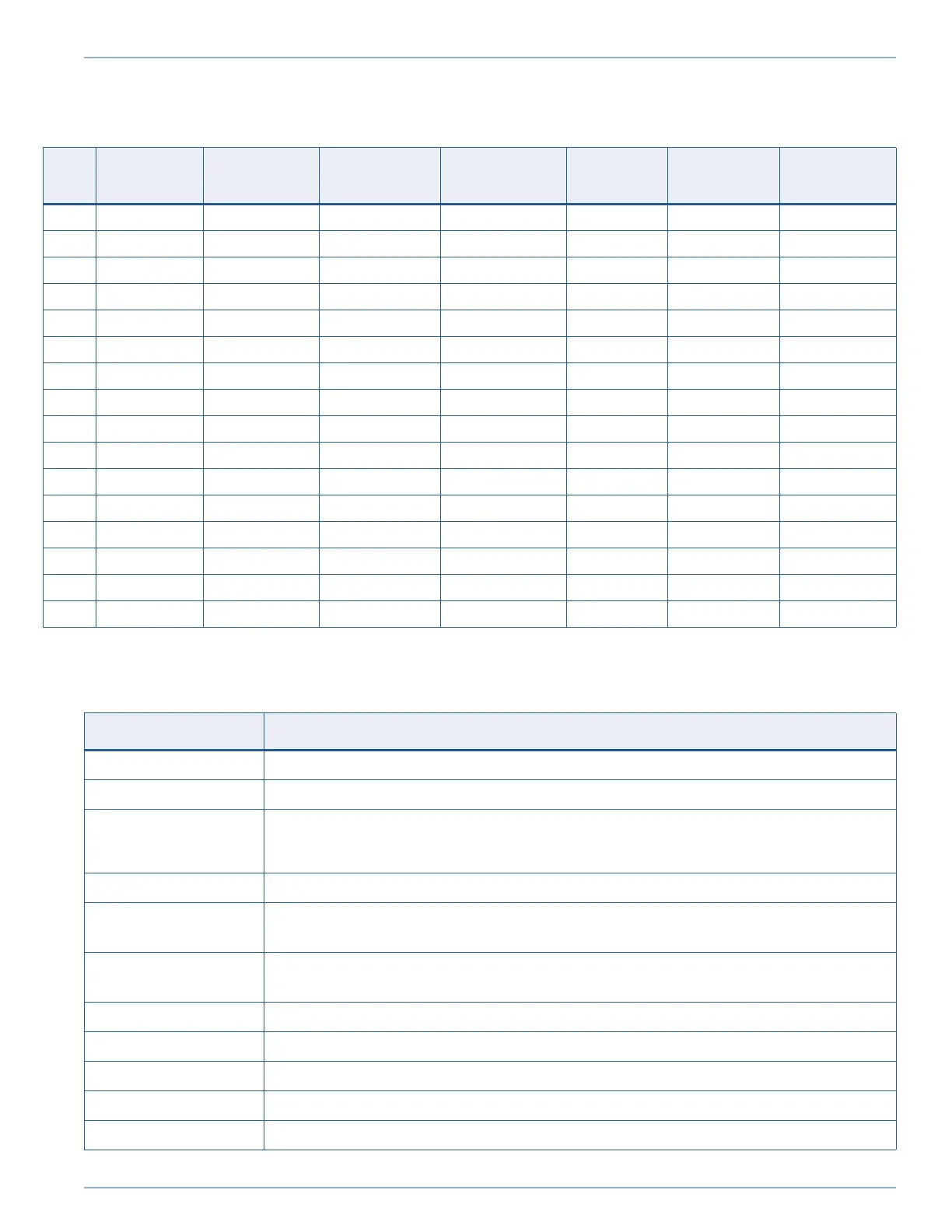

Table A.16: P4 Basecard I/O Connector Signal Definitions

CHAMP-AV8 Signal Description

JTSEL_L JTAG Select Signal; pulled up to 3.3V on-board.

JPROC[3:0] Select JTAG Mode; pulled up to 3.3V on-board.

PMI_TCK,PMI_TDO,

PMI_TDI, PMI_TMS,

PMI_TRST_L

Reserved for Curtiss-Wright use.

PMI_JTSEL_L Reserved for Curtiss-Wright use.

PMBUS_SDA,

PMBUS_SCL

I

2

C interface to power regulators only.

IPMI_SERIAL_OUT,

IPMI_SERIAL_IN

Reserved for Curtiss-Wright use.

IPMI FPGA debug - LVTTL UART interface. No Connect on production units

CF_NVRAM_WR_DIS_L NVRAM Write Disable

CF_FLASH_WR_DIS_L Flash Write Disable

CF_PABS_WR_EN_L PABs Write Enable

CF_NAND_WR_DIS_L NAND Flash Write Disable

CF_PROM_WR_EN_L PROM Write Enable

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...