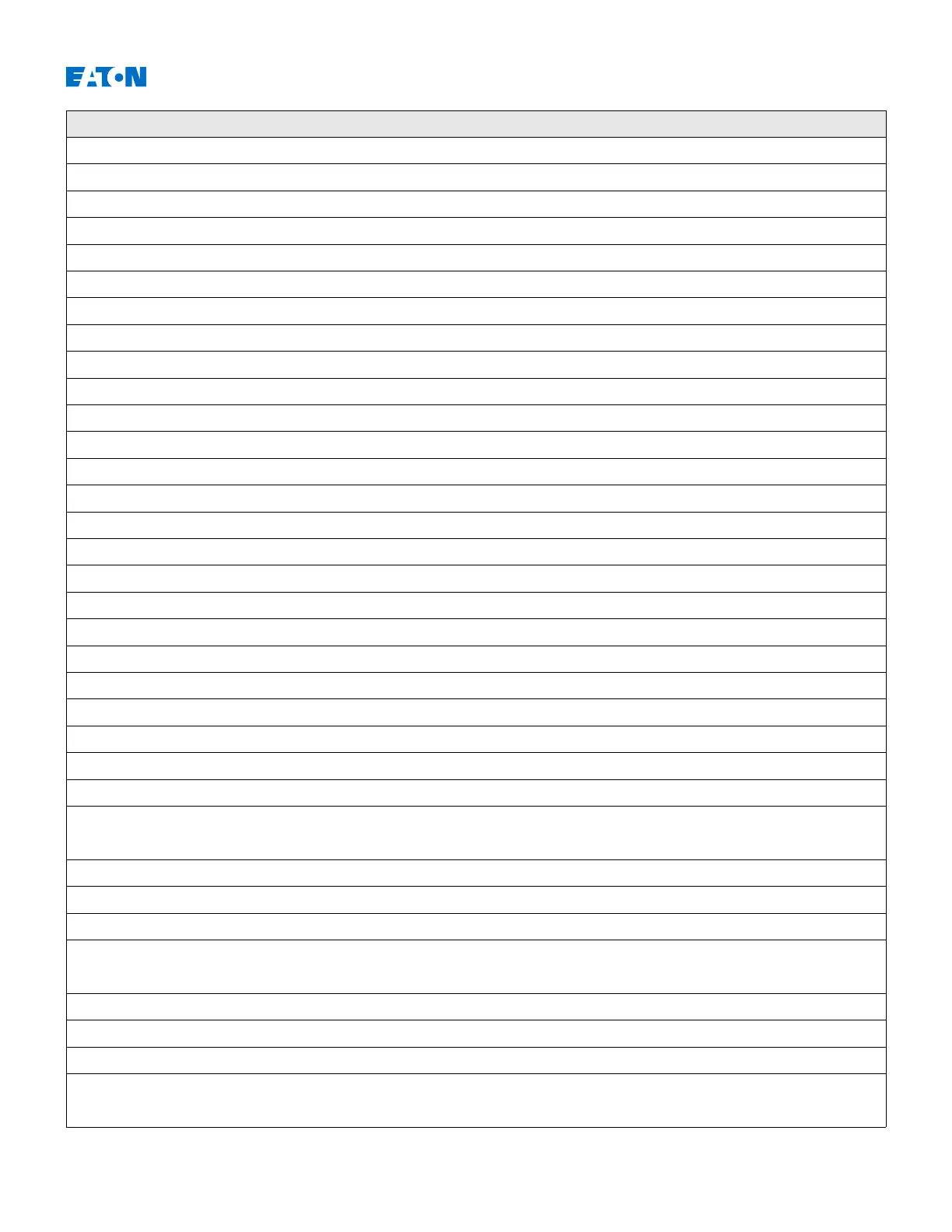

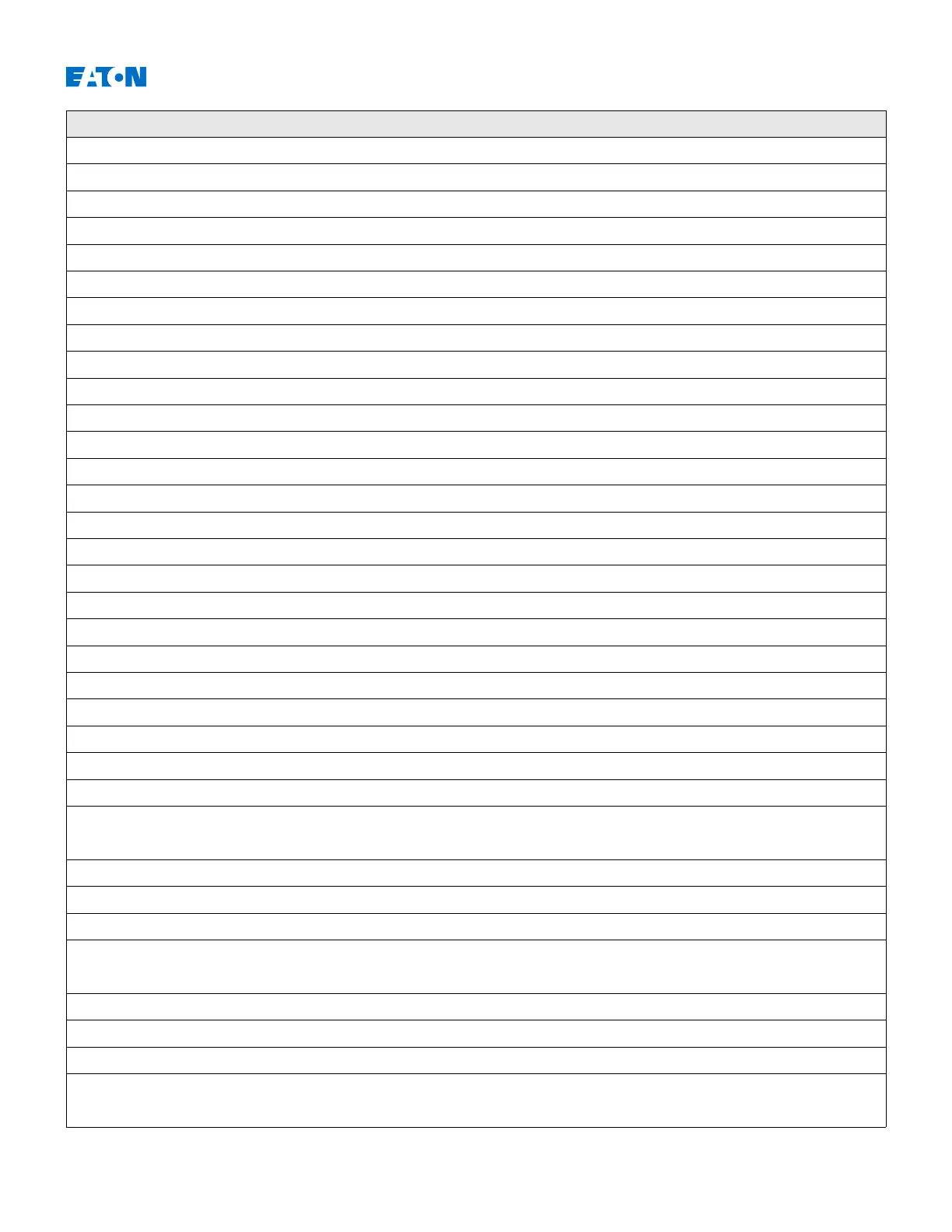

EDR-3000 IM02602003E

Name Description

Logic.LE6.Out Signal: Latched Output (Q)

Logic.LE6.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE7.Gate Out Signal: Output of the logic gate

Logic.LE7.Timer Out Signal: Timer Output

Logic.LE7.Out Signal: Latched Output (Q)

Logic.LE7.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE8.Gate Out Signal: Output of the logic gate

Logic.LE8.Timer Out Signal: Timer Output

Logic.LE8.Out Signal: Latched Output (Q)

Logic.LE8.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE9.Gate Out Signal: Output of the logic gate

Logic.LE9.Timer Out Signal: Timer Output

Logic.LE9.Out Signal: Latched Output (Q)

Logic.LE9.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE10.Gate Out Signal: Output of the logic gate

Logic.LE10.Timer Out Signal: Timer Output

Logic.LE10.Out Signal: Latched Output (Q)

Logic.LE10.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE11.Gate Out Signal: Output of the logic gate

Logic.LE11.Timer Out Signal: Timer Output

Logic.LE11.Out Signal: Latched Output (Q)

Logic.LE11.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE12.Gate Out Signal: Output of the logic gate

Logic.LE12.Timer Out Signal: Timer Output

Logic.LE12.Out Signal: Latched Output (Q)

Logic.LE12.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE13.Gate Out Signal: Output of the logic gate

Logic.LE13.Timer Out Signal: Timer Output

Logic.LE13.Out Signal: Latched Output (Q)

Logic.LE13.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE14.Gate Out Signal: Output of the logic gate

Logic.LE14.Timer Out Signal: Timer Output

Logic.LE14.Out Signal: Latched Output (Q)

Logic.LE14.Out inverted Signal: Negated Latched Output (Q NOT)

Logic.LE15.Gate Out Signal: Output of the logic gate

Logic.LE15.Timer Out Signal: Timer Output

Logic.LE15.Out Signal: Latched Output (Q)

www.eaton.com 330

Loading...

Loading...