EDGECORE NETWORKS CORPORATION 2018

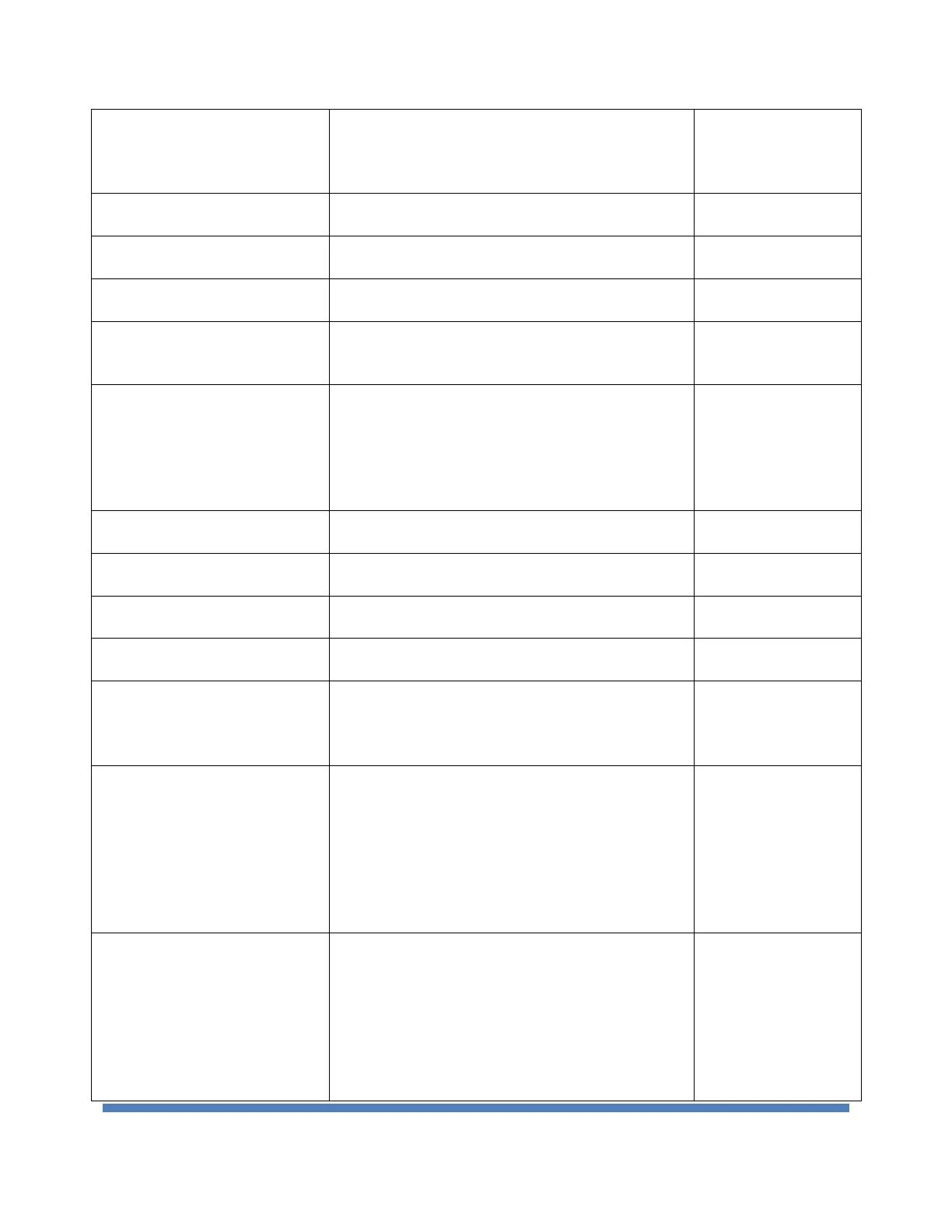

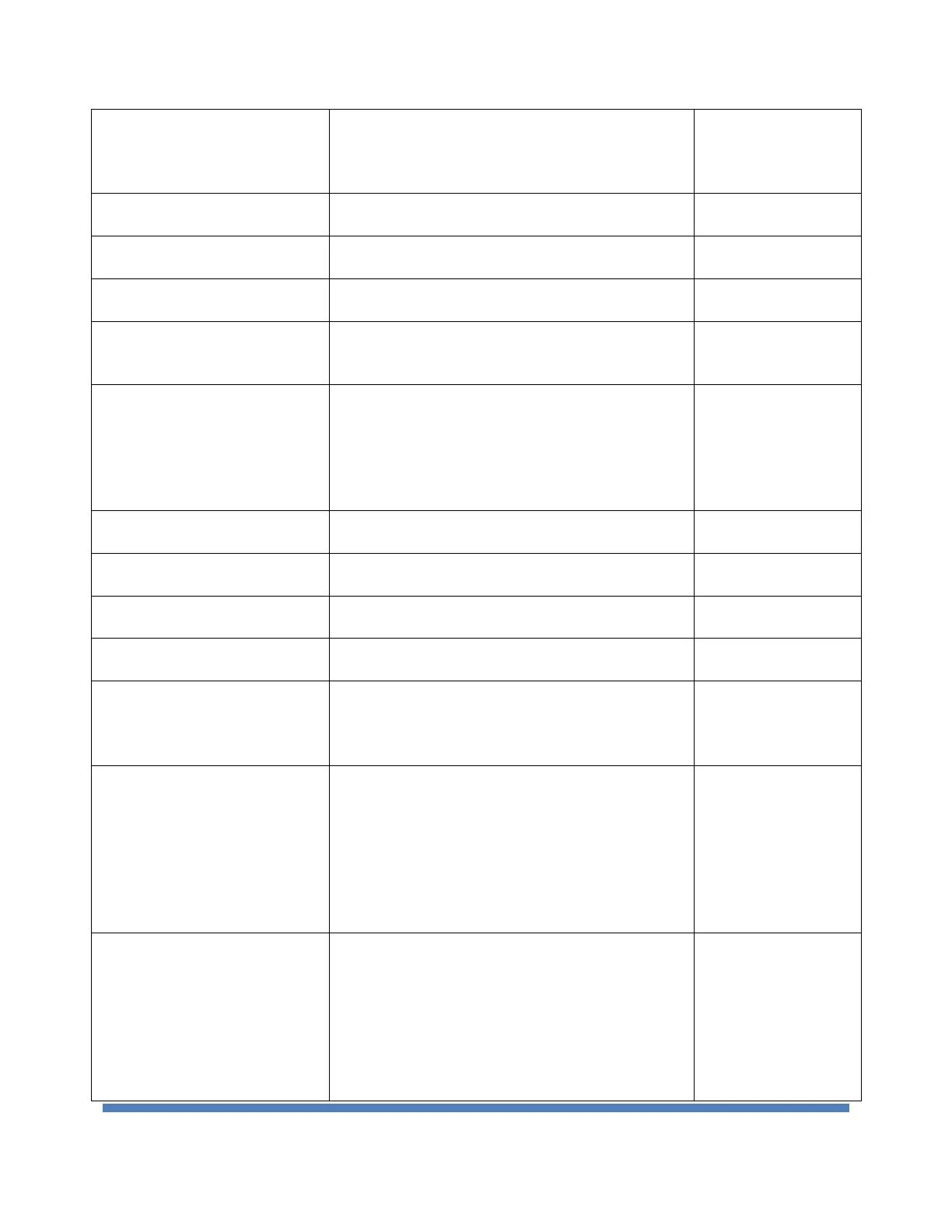

address lines (A16, A17, A18, A19, or A20) as

selected in Top-Swap Block size soft strap

(handled through FITc.

1 = Disable “Top Swap” mode.

This pin must not be driven low until after rising

edge of RSMRST_N.

This pin must not be driven low until after rising

edge of RSMRST_N.

This pin must not be driven low until after rising

edge of RSMRST_N.

Build-in Self Test (BIST) enable strap:

0 = BIST Disable

1 = BIST Enable

Integrated Service Processor Boot Mode

Selection:

0 = Integrated Service Processor Boot Mode

Disabled.

1 = Integrated Service Processor Boot Mode

Enable

0 = The platform is not Intel TXT enabled.

1 = Default. The platform is Intel TXT enabled.

0 = Default. The SoC is not the Intel TXT Agent.

1 = The SoC is the Intel TXT Agent.

0 = Safe Mode Boot Disabled

1 = Safe Mode Boot Enabled

0 = Debug Mode

1 = Normal Mode

Select between DDR4 and DDR3

0 = DDR3, it requires <1K ohm pull down in order

to out drive the internal pull up.

1= DDR4 (Default)

In micro-server design space, there will be

multiple sockets

that share a PECI bus. However these sockets are

effectively

independent agents. The PECI IDs are used as

straps to

identify which socket is which in order for PECI

bus to work.

LAN_MDIO_DIR_CTL_0;

LAN_MDIO_DIR_CTL_1

00 = Both LAN ports are disabled. Note: In this

mode manageability is not functional and must

not be enabled in NVM control word 1.

01 = Port 1 is disabled. Port 0 is enabled.

10 = Reserved

11 = Both Port 0 and 1 are enabled. Recommend

5.1K ohm pull up to VCCIOIN or 5.1K ohm pull

down to GND.

Loading...

Loading...