EDGECORE NETWORKS CORPORATION 2018

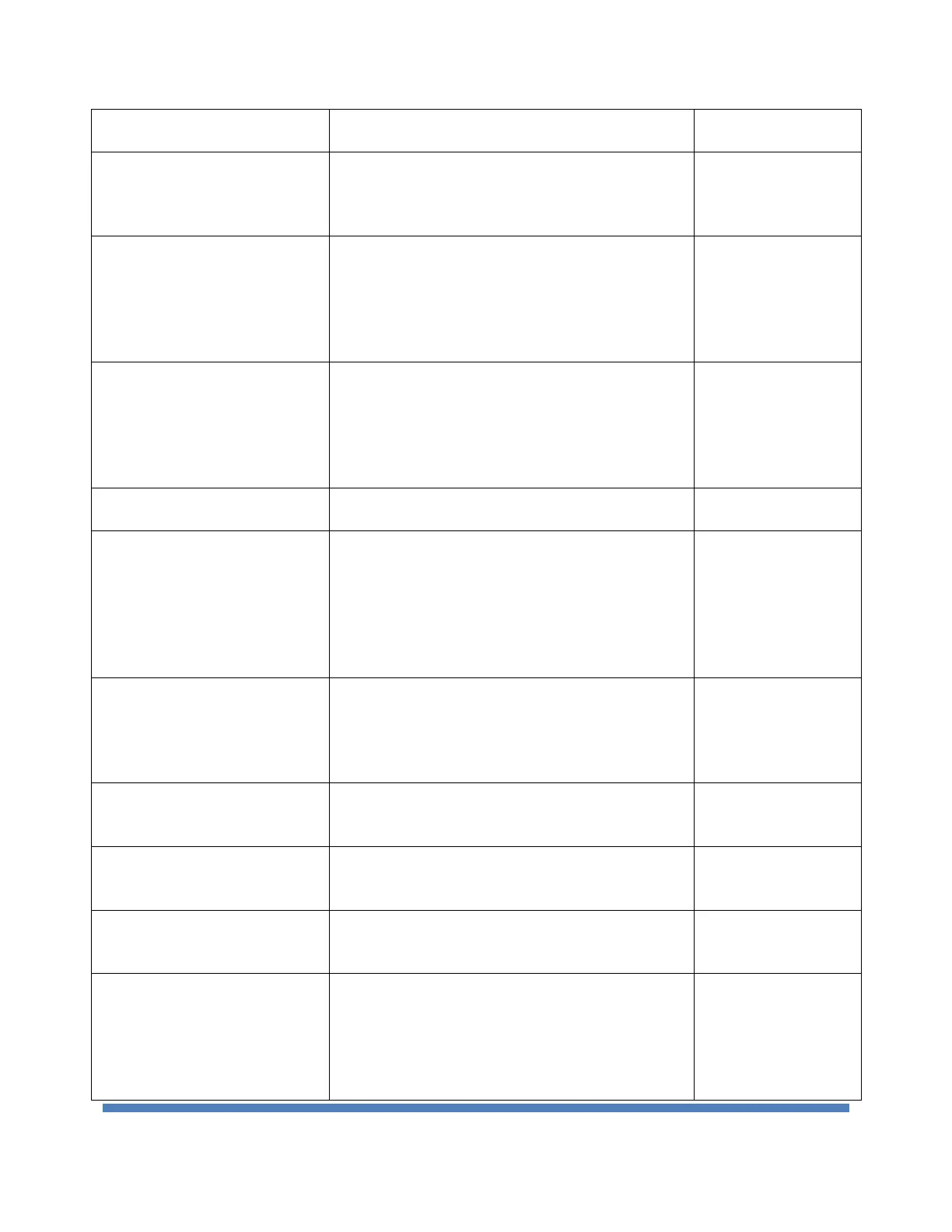

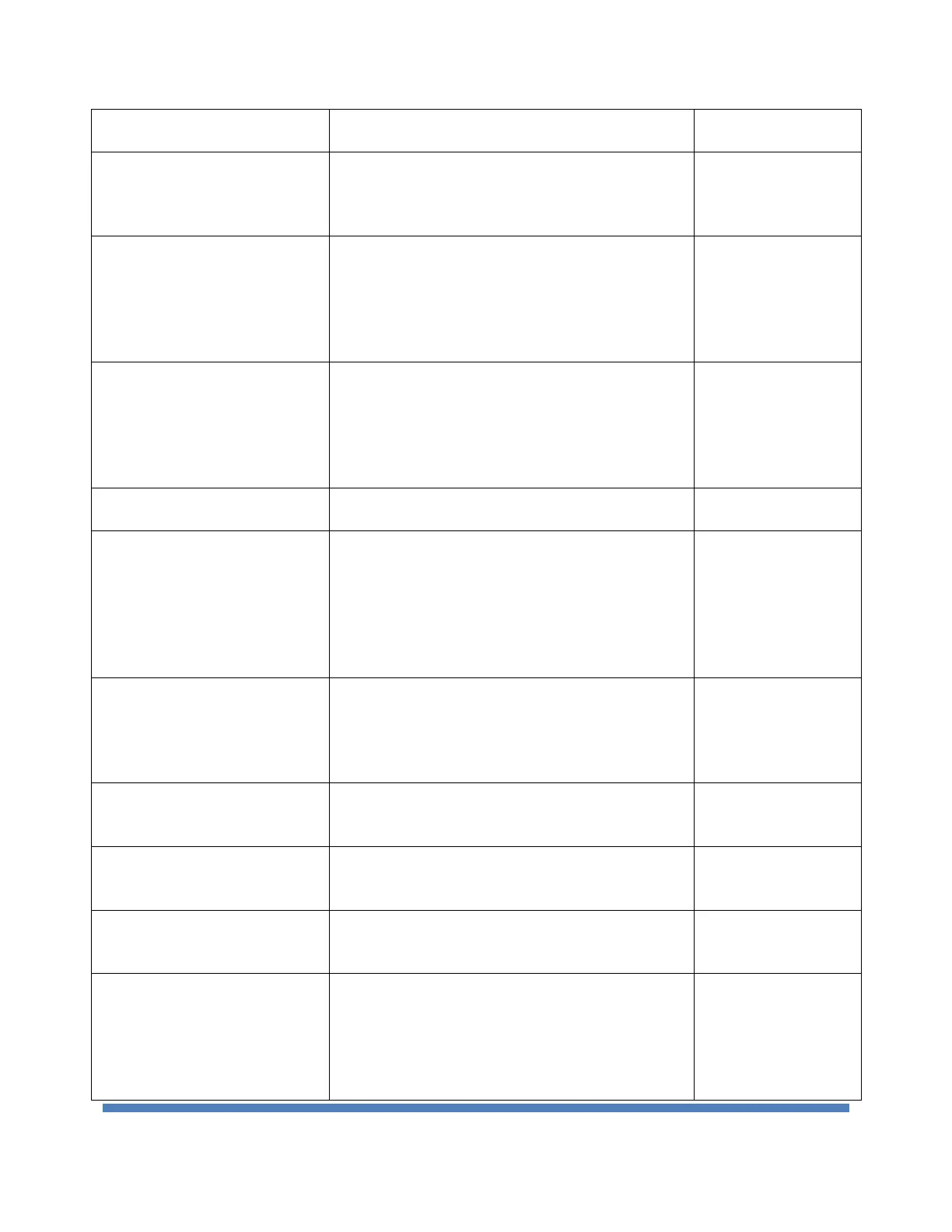

in conjunction with Boot BIOS Destination

Selection 0 strap.

0 = Disable Intel ME Crypto Transport Layer

Security (TLS) cipher suite (no confidentiality).

1 = Enable Intel ME Crypto Transport Layer

Security (TLS) cipher suite (with confidentiality).

0 = Enable security measures defined in the Flash

Descriptor.

1 = Disable Flash Descriptor Security (override).

This strap should only be asserted high using

external pull-up in manufacturing/debug

environments ONLY.

0 = DCPSUS1, DCPSUS2 and DCPSUS3 are

powered from an external power source (should

be connected to an external VRM). It should not

pull the strap low.

1 = Integrated VRMs enabled. DCPSUS1, DCPSUS2

and DCPSUS3 can be left as No Connect.

0 = Disable PLL On-Die voltage regulator.

1 = Enable PLL On-Die voltage regulator.

0 = Disable Integrated DeepSx Well (DSW) On-Die

Voltage Regulator. This mode is only supported

for testing environments.

1 = Enable DSW 3.3 V-to-1.05 V Integrated

DeepSx Well (DSW) On-Die Voltage Regulator.

This must always be pulled high on production

boards.

0 = Disable “No Reboot” mode.

1 = Enable “No Reboot” mode (integrated PCH

will disable the TCO Timer system reboot

feature). This function is useful

when running ITP/XDP.

0 = SoC RX is terminated to VSS. Grangeville

platform only supports SoC Rx terminated to VSS.

1 = SoC RX is terminated to VCC/2.

0 = SoC TX is terminated to VSS. Grangeville

platform only supports SoC Tx terminated to VSS

1 = SoC TX is terminated to VCC/2.

0 = SoC is in AC-coupling mode. Grangeville

platform only supports AC-coupling mode.

1 = SoC is in DC-coupling mode.

0 = Enable “Top Swap” mode. This inverts an

address on access to SPI and firmware hub, so the

processor believes its fetches the alternate boot

block instead of the original boot-block. PCH will

invert A16 (default) for cycles going to the upper

two 64 KB blocks in the FWH or the appropriate

Loading...

Loading...