EDGECORE NETWORKS CORPORATION 2018

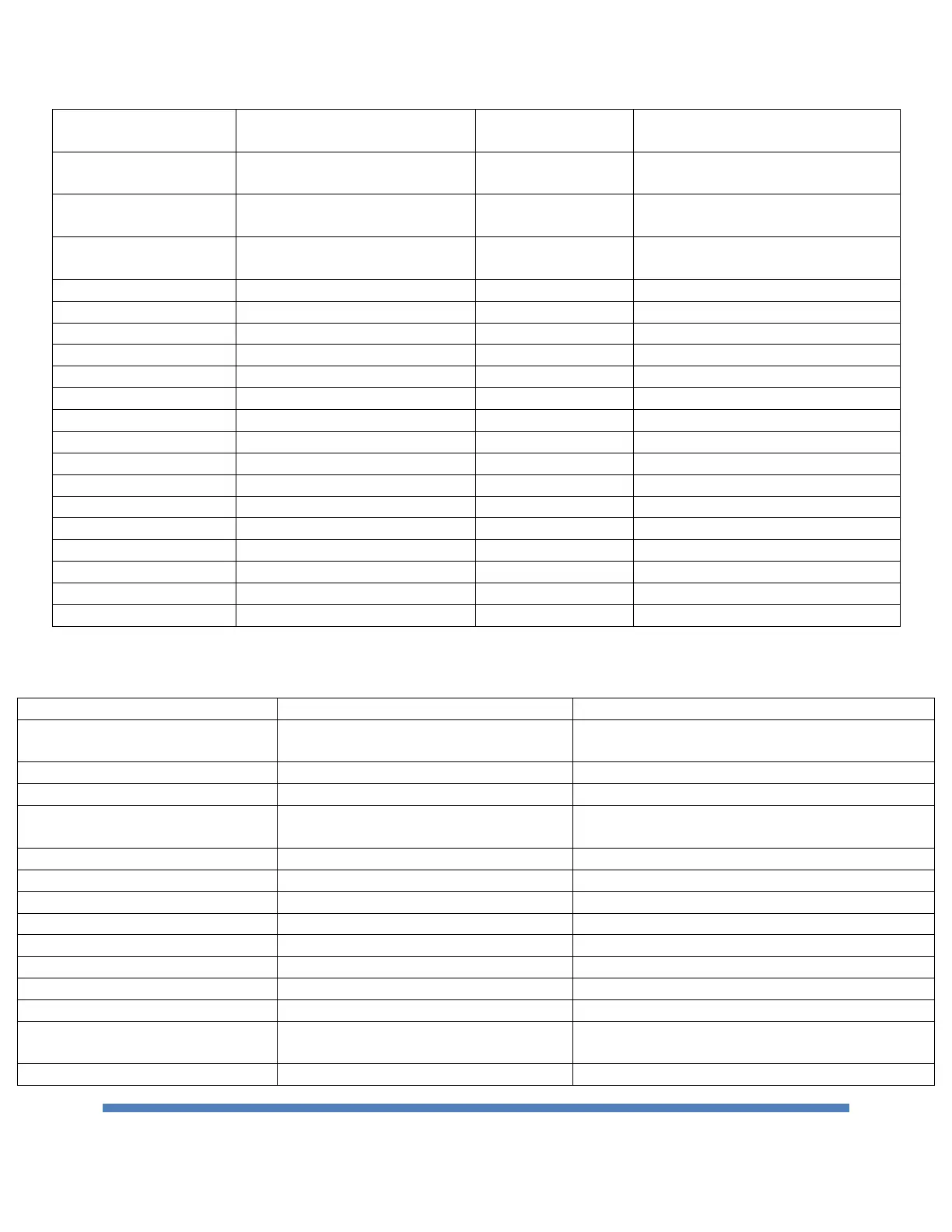

Anywhere in 64KB I/O space

1. SATA host controller #1, #2

2. IDE-R

Anywhere in 64KB I/O space

1. SATA host controller #1, #2

2. IDE-R

Anywhere in 64KB I/O space

1. SATA host controller #1, #2

2. IDE-R

Anywhere in 64KB I/O space

1. SATA host controller #1, #2

2. IDE-R

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

3 ranges in 64KB I/O space

8 ranges in 64KB I/O space

8 ranges in 64KB I/O space

2 ranges in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

Anywhere in 64KB I/O space

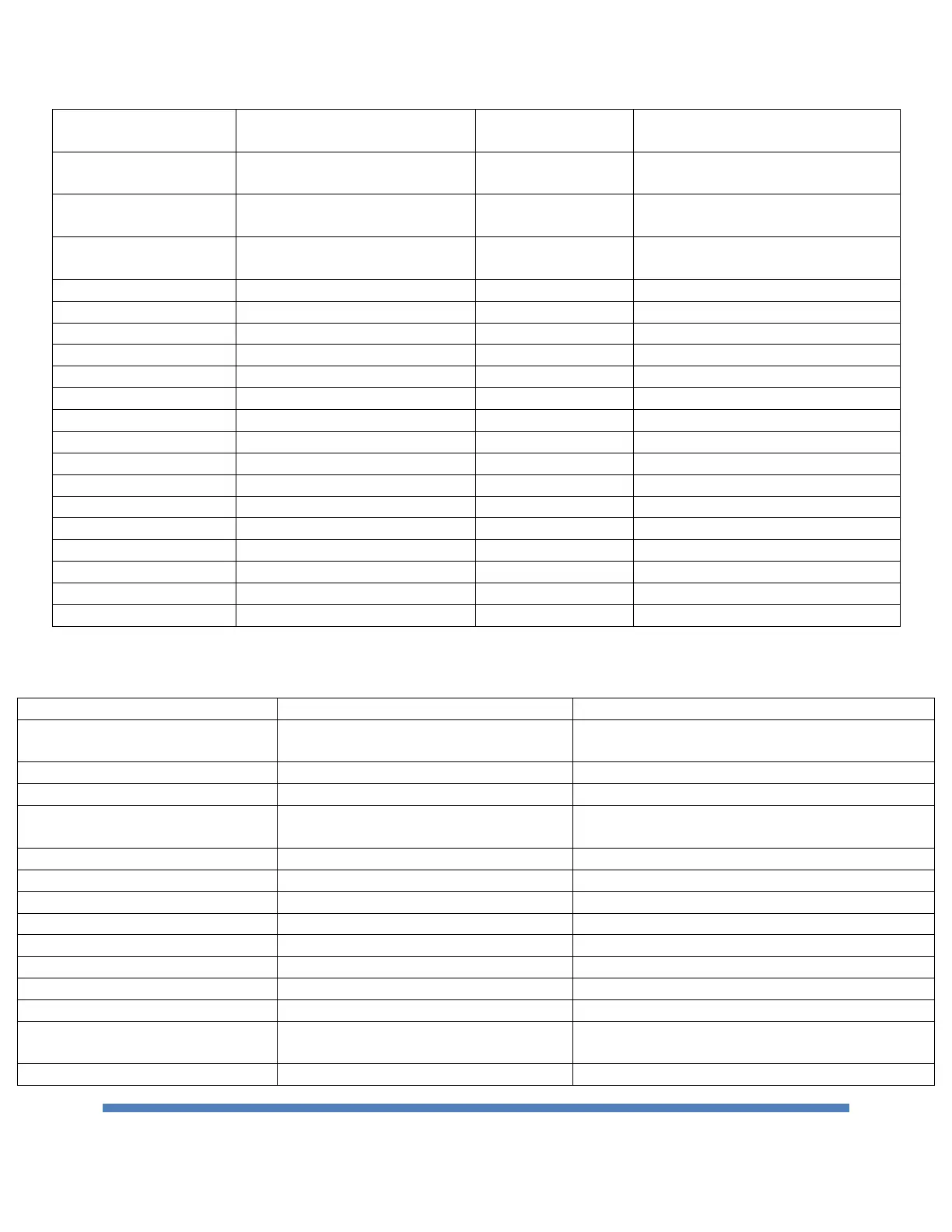

Table 8 Memory decode ranges from processor perspective

0000 0000h-000D FFFFh

0010 0000h-TOM

TOM registers in host controller

Bit 6 in BIOS decode enable register is set

Bit 7 in BIOS decode enable register is set

IOx APCI inside broadwell-de SoC

_ _ is controlled using APIC range select (ASEL)

field and APIC enable (AEN) bit.

PCI-E root port 1 I/OxAPIC enable (PAE) set

PCI-E root port 2 I/OxAPIC enable (PAE) set

PCI-E root port 3 I/OxAPIC enable (PAE) set

PCI-E root port 4 I/OxAPIC enable (PAE) set

PCI-E root port 5 I/OxAPIC enable (PAE) set

PCI-E root port 6 I/OxAPIC enable (PAE) set

PCI-E root port 7 I/OxAPIC enable (PAE) set

PCI-E root port 8 I/OxAPIC enable (PAE) set

FFC0 0000h-FFC7 FFFFh

FF80 0000h- FF87 FFFFh

Bit 8 in BIOS decode enable register is set

Bit 9 in BIOS decode enable register is set

Loading...

Loading...