EDGECORE NETWORKS CORPORATION 2018

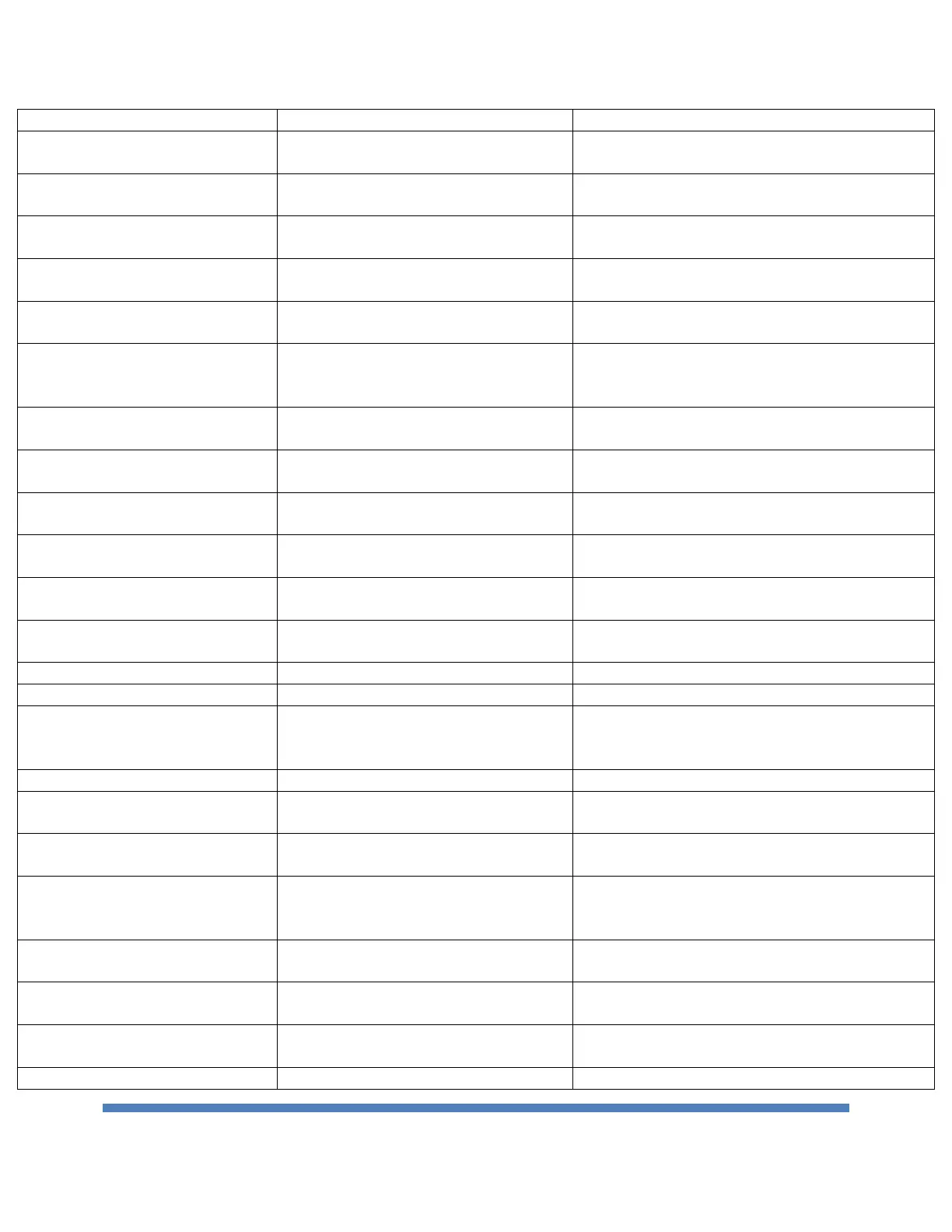

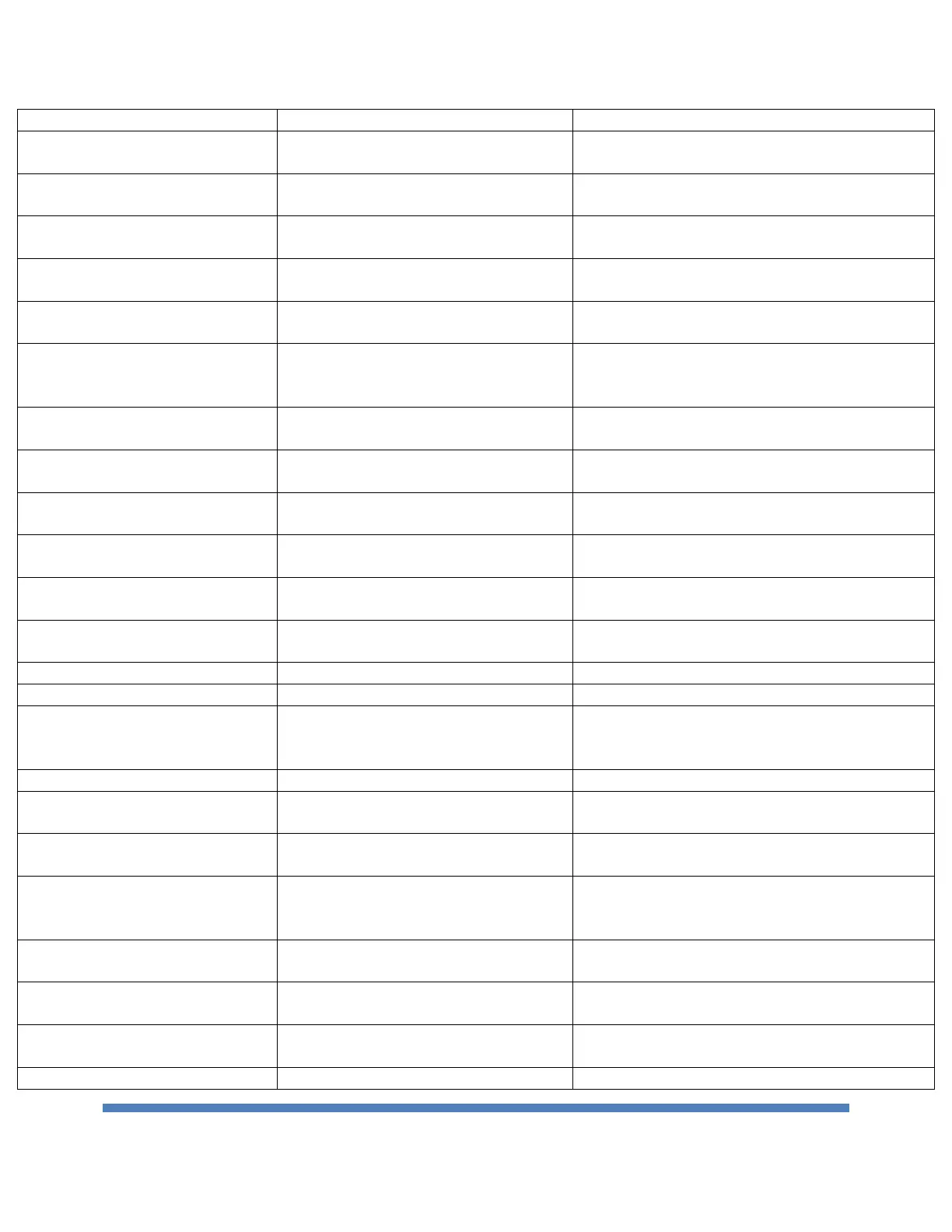

FFD0 0000h-FFD7 FFFFh

FF90 0000h- FF97 FFFFh

Bit 10 in BIOS decode enable register is set

FFD8 0000h-FFDF FFFFh

FF98 0000h- FF9F FFFFh

Bit 11 in BIOS decode enable register is set

FFE0 0000h-FFE7 FFFFh

FFA0 0000h- FFA7 FFFFh

Bit 12 in BIOS decode enable register is set

FFE8 0000h-FFEF FFFFh

FFA8 0000h- FFAF FFFFh

Bit 13 in BIOS decode enable register is set

FFF0 0000h-FFF7 FFFFh

FFB0 0000h-FFB7 FFFFh

Bit 14 in BIOS decode enable register is set

FFF8 0000h–FFFF FFFFh

FFB8 0000h–FFBF FFFFh

Always enabled.

The top two 64KB blocks of this range can be

swapped.

FF70 0000h–FF7F FFFFh

FF30 0000h–FF3F FFFFh

Bit 3 in BIOS Decode Enable register is set

FF60 0000h–FF6F FFFFh

FF20 0000h–FF2F FFFFh

Bit 2 in BIOS Decode Enable register is set

FF50 0000h–FF5F FFFFh

FF10 0000h–FF1F FFFFh

Bit 1 in BIOS Decode Enable register is set

FF40 0000h–FF4F FFFFh

FF00 0000h–FF0F FFFFh

Bit 0 in BIOS Decode Enable register is set

128 KB anywhere in 4 GB range

Integrated LAN Controller

Enable using BAR in D25:F0 (Integrated LAN

Controller MBARA)

4 KB anywhere in 4 GB range

Integrated LAN Controller

Enable using BAR in D25:F0 (Integrated LAN

Controller MBARB)

1 KB anywhere in 4 GB range

Enable using standard PCI mechanism (D29:F0)

64 KB anywhere in 4 GB range

Enable using standard PCI mechanism (D20:F0)

High Precision Event

Timers

BIOS determines the “fixed” location which is

one of four, 1-KB ranges where X (in the first

column) is 0h, 1h, 2h, or 3h.

Memory Base/Limit anywhere in 4

GB range

Enable using standard PCI mechanism (D30:F0)

Prefetchable Memory Base/Limit

anywhere in 64-bit address range

Enable using standard PCI mechanism (D30:F0)

64 KB anywhere in 4 GB range

LPC Generic Memory Range. Enable using setting

bit[0] of the LPC Generic Memory Range register

(D31:F0:offset 98h).

32 Bytes anywhere in 64-bit

address range

Enable using standard PCI mechanism (D31:F3)

2 KB anywhere above 64 KB to

4 GB range

AHCI memory-mapped registers. Enable using

standard PCI mechanism (D31:F2)

Memory Base/Limit anywhere in 4

GB range

PCI Express* Root Ports 1-8

Enable using standard PCI mechanism (D28: F 0-

7)

Prefetchable Memory Base/Limit

PCI Express Root Ports 1-8

Enable using standard PCI mechanism (D28:F 0-7)

Loading...

Loading...