EDGECORE NETWORKS CORPORATION 2018

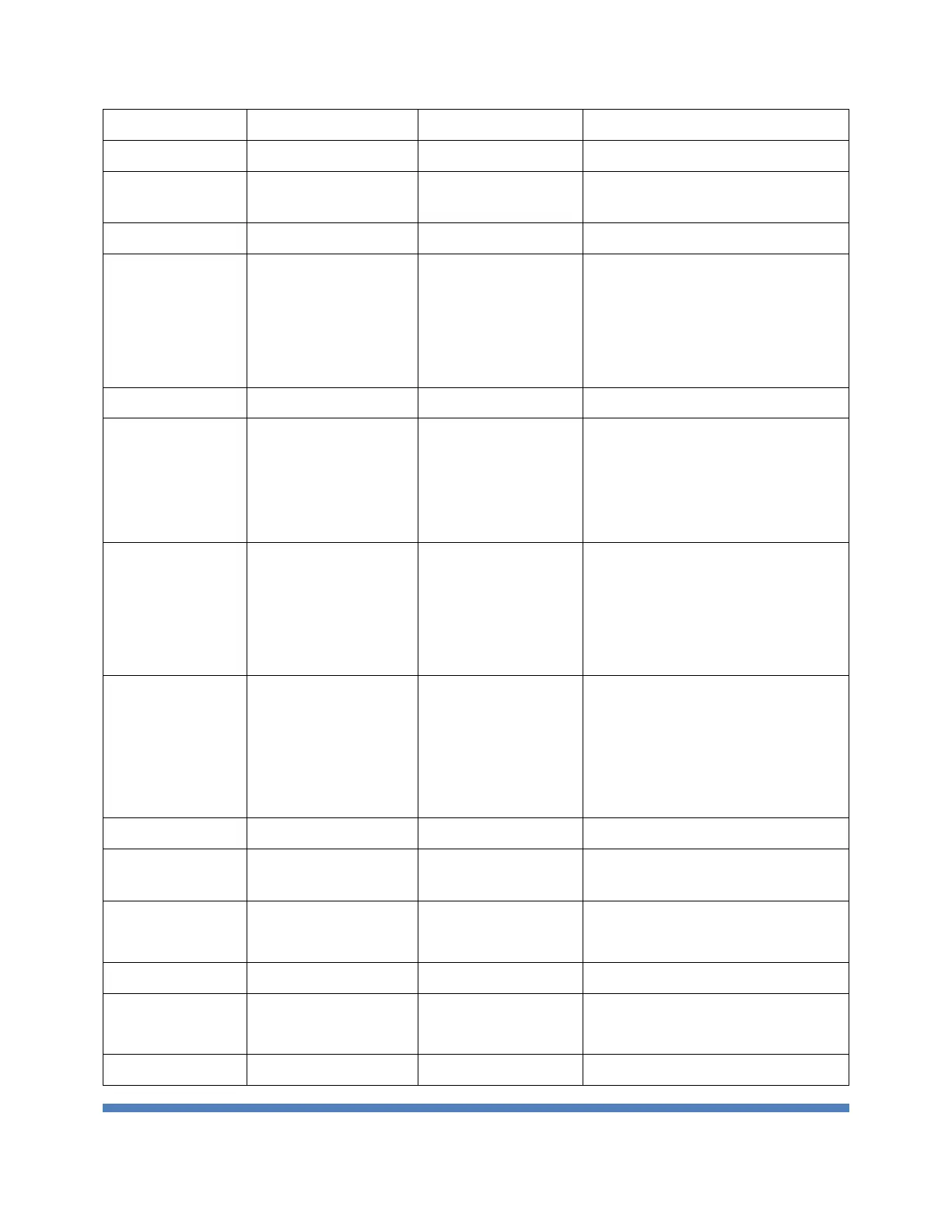

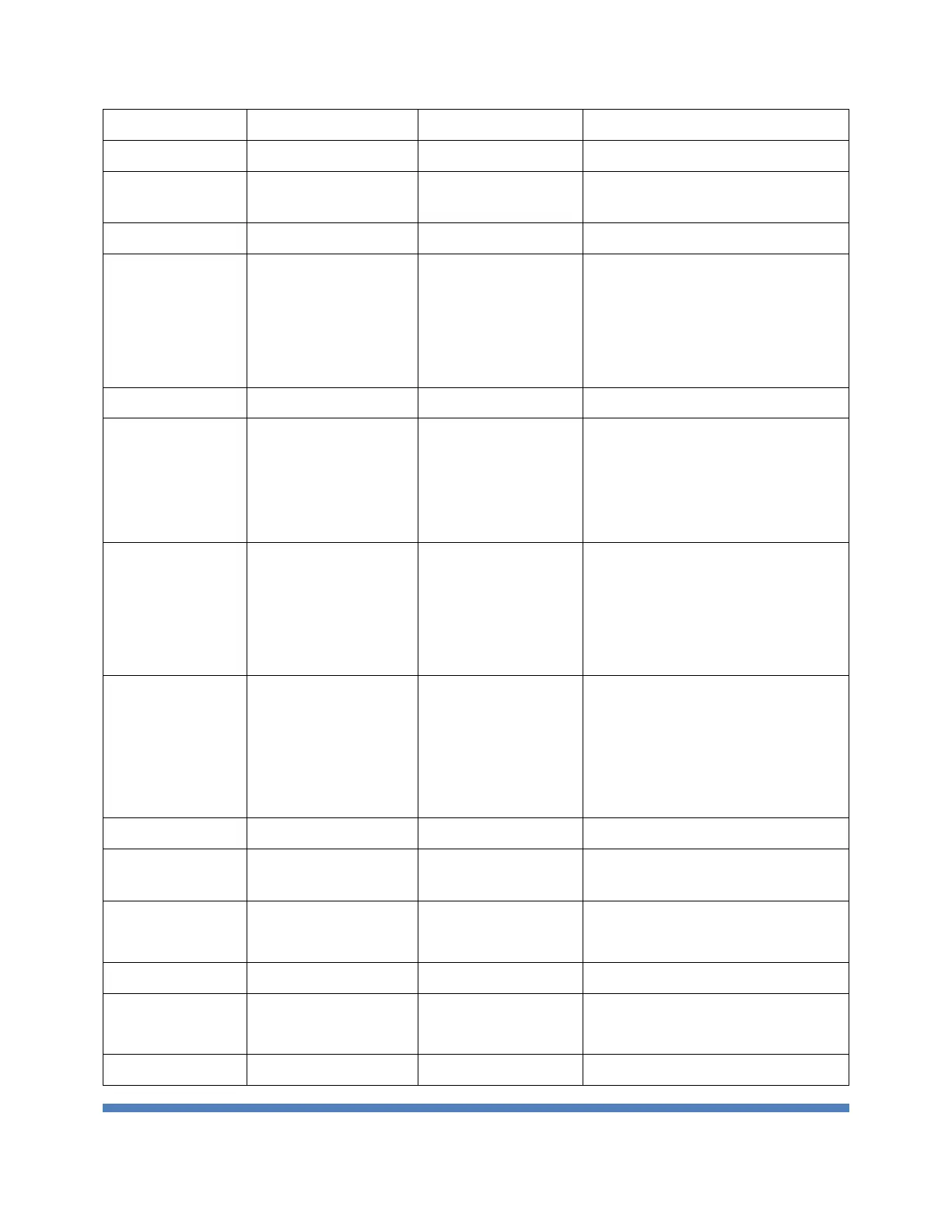

CPU to PCH Throttle event

interrupt

JTAG enable, enable JTAG

multiplexer to update CPLD code

from CPU.

1: enable the JTAG multiplexer

0: disable the JTAG multiplexer

JTAG Multiplexer select, which

select the JTAG signals from CPU

would go to CPLD or main board

1: to CPLD (default)

0: to Main board

XDP_NOA5_PCH/

BDX_CPLD_JTAG_TDI

When configure to be

BDX_CPLD_JTAG_TDI, which is CPU

JTAG output

XDP_NOA6_PCH/

BDX_CPLD_JTAG_TDO

When this pin configure to

BDX_CPLD_JTAG_TDO

, which is CPU JTAG input

Reset MAC, to do the sleep

function.

XDP_NOA7_PCH/

BDX_CPLD_JTAG_TCK

FM_THROTTLE_PCH_N/

FM_THROTTLE_N

Loading...

Loading...