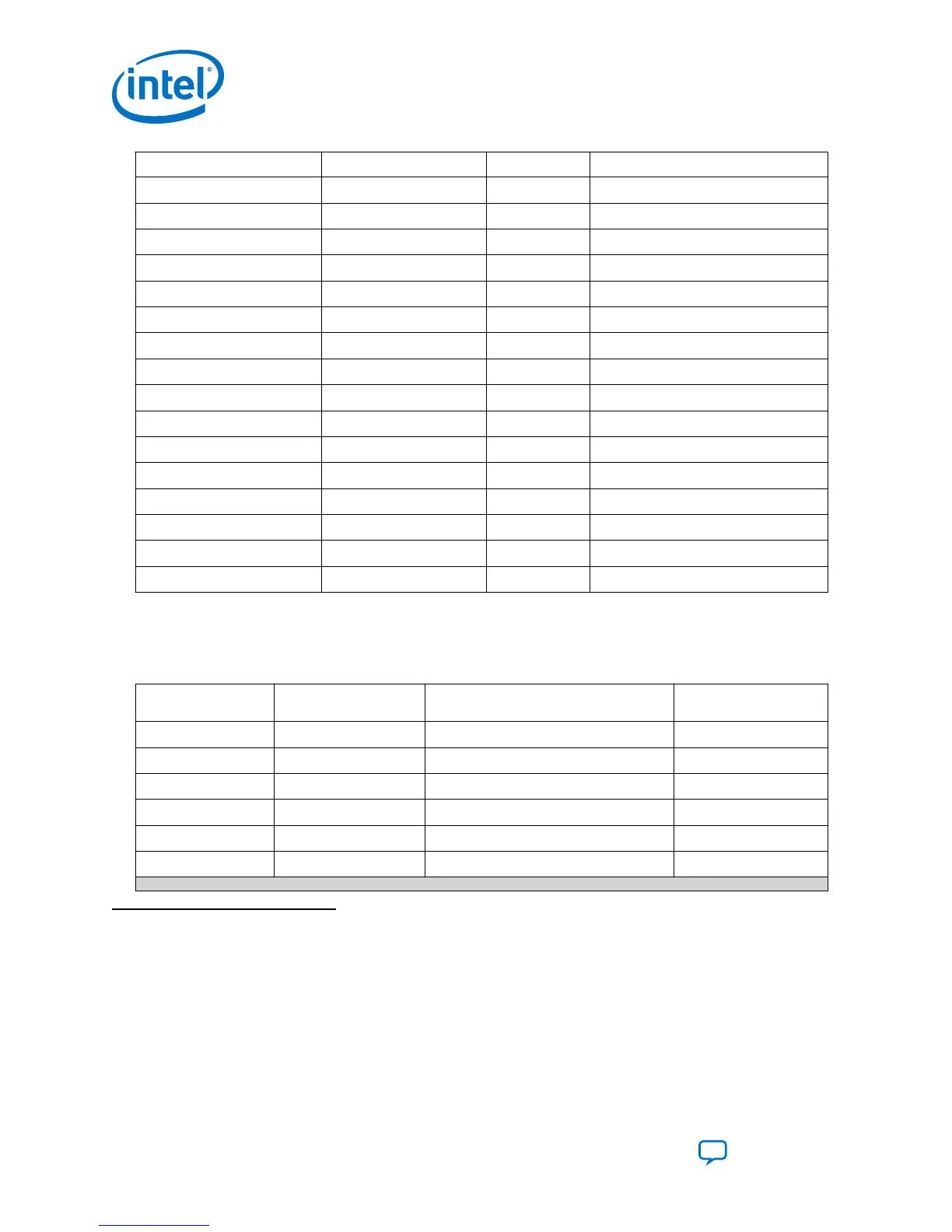

Configuration Function Configuration Scheme Direction Powered by

CONF_DONE

(6)

All schemes Output V

CCIO_SDM

INIT_DONE

(7)

All schemes Output V

CCIO_SDM

OSC_CLK_1

All schemes Input V

CCIO_SDM

AS_nCSO[3:0]

AS Output V

CCIO_SDM

AS_DATA[3:0]

AS Bidirectional V

CCIO_SDM

AS_CLK

AS Output V

CCIO_SDM

AVST_READY

Avalon-ST x8/x16/32 Output V

CCIO_SDM

AVSTx8_DATA[7:0]

Avalon-ST x8 Input V

CCIO_SDM

AVSTx8_VALID

Avalon-ST x8 Input V

CCIO_SDM

AVSTx8_CLK

Avalon-ST x8 Input V

CCIO_SDM

AVST_DATA[31:0]

(8)

Avalon-ST x16/x32 Input V

CCIO

AVST_VALID

(8)

Avalon-ST x16/x32 Input V

CCIO

AVST_CLK

(8)

Avalon-ST x16/x32 Input V

CCIO

SDMMC_CFG_CMD

SD/MMC Output V

CCIO_SDM

SDMMC_CFG_DATA[7:0]

SD/MMC Bidirectional V

CCIO_SDM

SDMMC_CFG_CCLK

SD/MMC Output V

CCIO_SDM

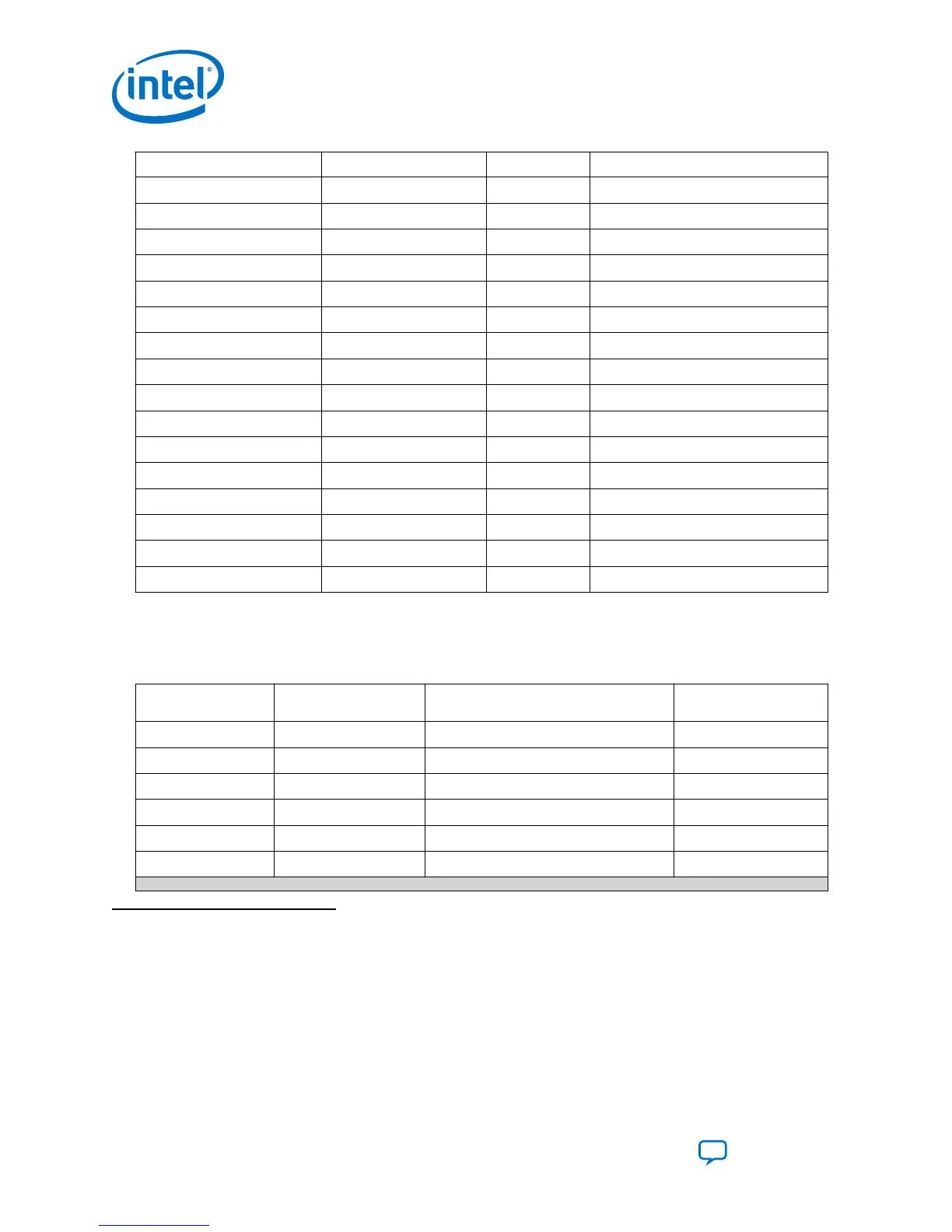

2.4.3.1. Configuration Pins I/O Standard and Drive Strength

Table 6. Intel Stratix 10 Configuration Pins I/O Standard and Drive Strength

Configuration Pin

Function

Direction I/O Standard Drive Strength (mA)

TDO

Output 1.8V LVCMOS 8

TMS

Input Schmitt Trigger Input —

TCK

Input Schmitt Trigger Input —

TDI

Input Schmitt Trigger Input —

nSTATUS

Output 1.8V LVCMOS 8

OSC_CLK_1

Input Schmitt Trigger Input —

continued...

(5)

The MSEL[2:0] pins are dual purpose. You can assign any unused MSEL[2:0] pin to other

functions such as power management or non-dedicated configuration pins.

(6)

You enable the CONF_DONE pin function in the Intel Quartus Prime Software. The Avalon-ST

configuration scheme using the Parallel Flash Loader (PFL) II requires this pin.

(7)

You enable the INIT_DONE pin function in the Intel Quartus Prime Software. This pin is

optional for all configuration schemes.

(8)

These are dual purpose configuration pins. You can use these pins as GPIOs in user mode.

2. Intel Stratix 10 Configuration Details

UG-S10CONFIG | 2018.11.02

Intel Stratix 10 Configuration User Guide

Send Feedback

20

Loading...

Loading...