6. Intel Stratix 10 Debugging Guide

6.1. Intel Stratix 10 Debugging Overview

Intel Stratix 10 devices employ a new configuration architecture. The Secure Device

Manager (SDM), a dedicated hard processor, controls and monitors all aspects of

device configuration from device power-on reset. This configuration architecture

differs from previous Intel FPGA device families where state machines control

configuration.

There are important differences between Intel Stratix 10 and previous device families

with respect to available configuration modes, configuration pin behavior, and

connection guidelines. In addition, the bitstream format is different. Knowing about

these differences and how these pins behave can help you understand and debug

configuration issues.

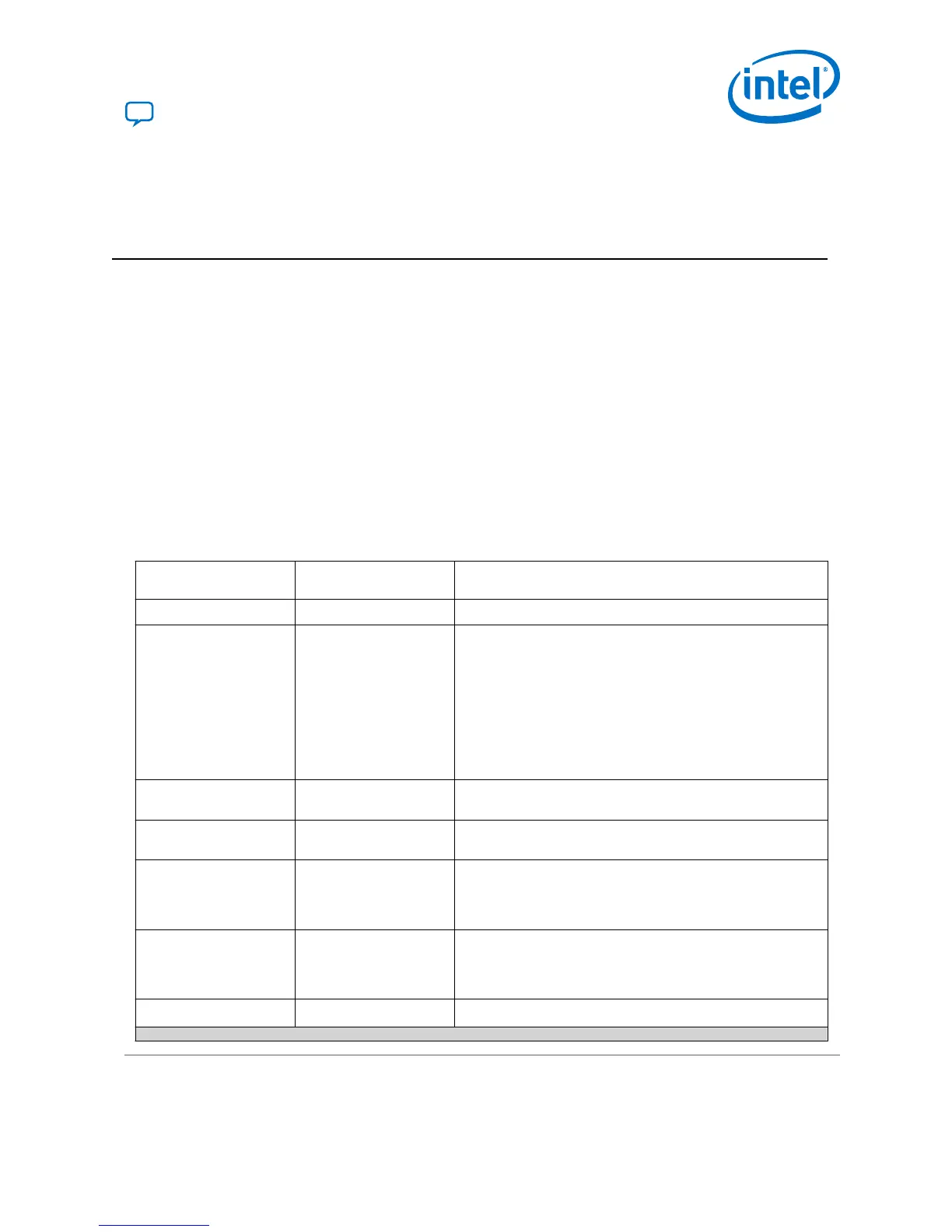

6.2. Configuration Pin Differences from Previous Device Families

Configuration Pin Names

(Pre-Intel Stratix 10)

Intel Stratix 10 Pin

Names

Notes

TRST

Not Available

Use the TMS reset sequence. Hold TMS high for 5 TCK cycles.

CLKUSR OSC_CLK_1

An external source you can supply to increase the configuration

throughput to 250 MHz. Using an external clock source

Transceivers, the HPS, PCIe, and the High Bandwidth Memory

(HBM2) require you this external clock.

• 25

• 100

• 125

Refer to Setting Configuration Clock Source for instructions on

setting the clock source and frequency in the Intel Quartus Prime

Pro Edition software.

CRC_ERROR

Any unused SDM_IO

(SEU_ERROR)

No dedicated location. Now called SEU_ERROR. Ignore until after

CONF_DONE asserts.

CONF_DONE SDM_IO5, SDM_IO16

(CONF_DONE)

No single dedicated pin location. No longer Open Drain. External

pull-up Is not mandatory.

DCLK (PS - FPP)

AVST_CLK, AVSTx8_CLK

x8 mode has a dedicated clock input on SDM_IO14

(AVSTx8_CLK). For other Avalon-ST modes, use AVST_CLK.

AVST_CLK and AVSTx8_CLK must be continuous and cannot

pause during configuration.

DCLK (AS)

SDM_IO2 (AS_CLK) When using the internal oscillator in AS mode, the AS_CLK runs

in the range of 57 - 75 MHz. If you provide a 25 MHz, 100 MHz

or 125 MHz clock to the OSC_CLK_1 pin, the AS_CLK can run up

to 133 MHz.

DEV_OE

Not Available

continued...

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus

and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other

countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Loading...

Loading...