Note: The SD MMC configuration scheme is not supported in the current release.

Related Information

• Supported CFI Flash Memory Devices on page 111

• Intel Stratix 10 GX and SX Device Family Pin Connection Guidelines

• AN 692: Power Sequencing Considerations for Intel Cyclone 10 GX, Intel Arria 10,

and Intel Stratix 10 Devices

• Device Configuration - Support Center

• Avalon Interface Specifications

• Intel Stratix 10 Configuration via Protocol (CvP) Implementation User Guide

• Intel Stratix 10 Device Datasheet (Core and HPS)

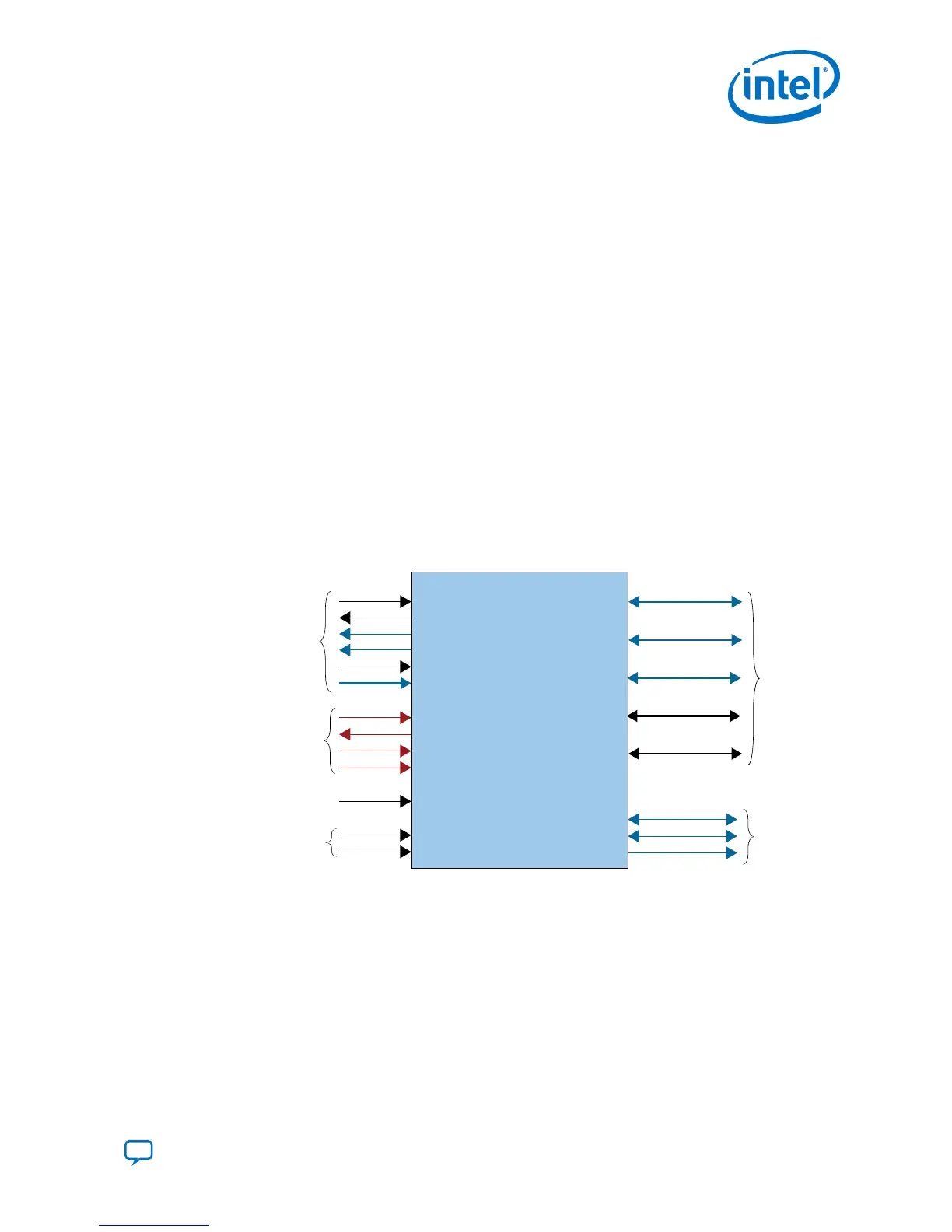

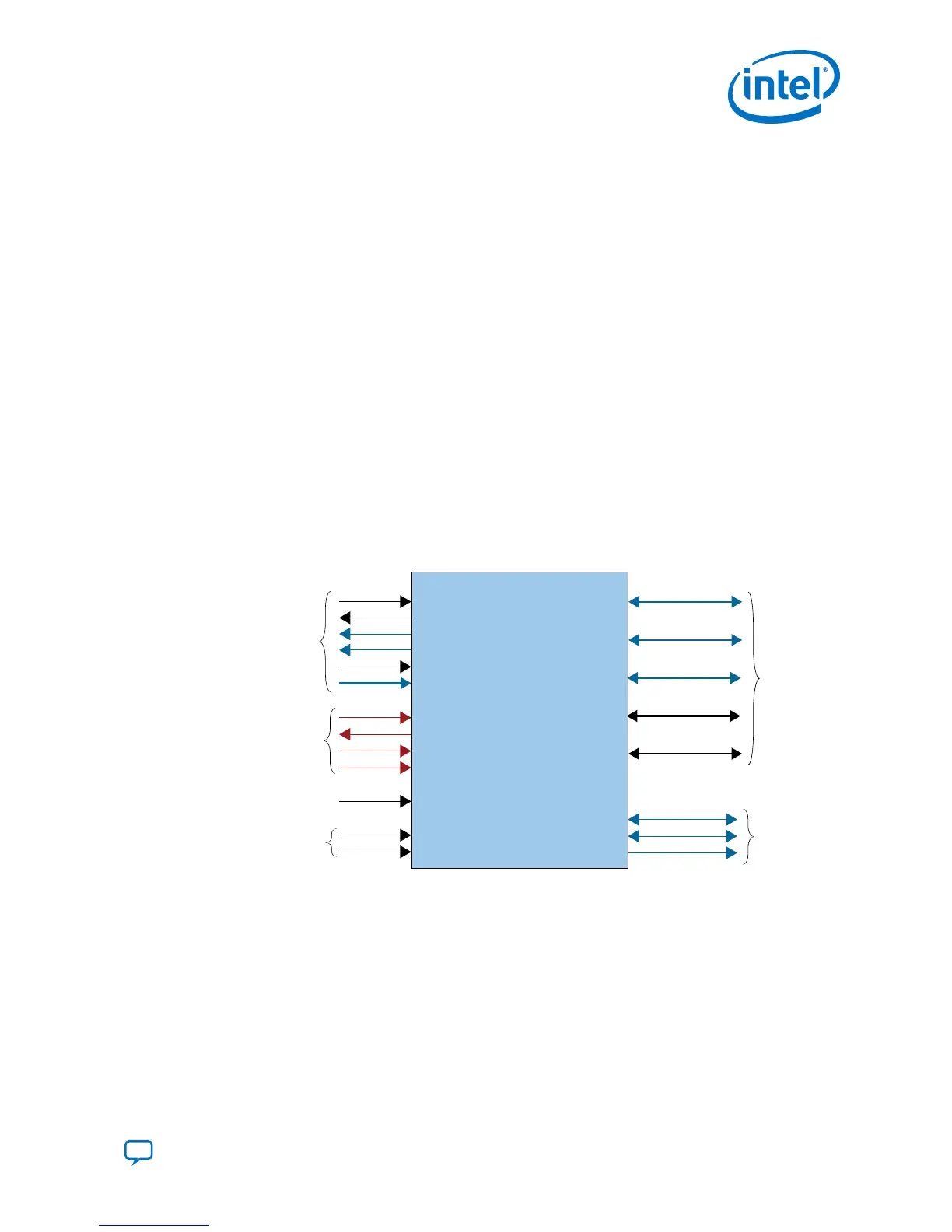

1.1.1. Configuration and Related Signals

The following figure shows the configuration interfaces and configuration-related

device functions. Pins shown in dark blue use dedicated SDM I/Os. Pins shown in black

use general purpose I/Os (GPIOs). Pins shown in red are dedicated JTAG I/Os. You

specify SDM I/O pin functions using the Device ➤ Configuration ➤ Device and Pin

Options dialog box in the Intel Quartus Prime software.

Figure 1. Intel Stratix 10 Configuration Interfaces

nCONFIG

nSTATUS

CONF_DONE

INIT_DONE

OSC_CLK_1

MSEL[2:0]

TCK

TDO

TMS

TDI

DIRECT_TO_FACTORY

VCCFUSEWR_SDM

VCCBAT

Intel Stratix 10

SDMCC

Avalon-ST x8

CvP

AS x4 (QSPI)

Configuration

Control

JTAG

Remote

System

Update (RSU)

Security

PWRMGT_SDA

PWRMGT_SCL

PWRMGT_ALERT

Smart

VID

Select

One

Avalon-ST x16 or x32

This user guide discusses most of the interfaces shown in the figure. Refer to the

separate Intel Stratix 10 Configuration via Protocol (CvP) Implementation User Guide

and Intel Stratix 10 Power Management User Guide for more information about those

features.

Related Information

• SDM Pin Mapping on page 17

• Intel Stratix 10 Configuration via Protocol (CvP) Implementation User Guide

• Intel Stratix 10 Power Management User Guide

1. Intel

®

Stratix

®

10 Configuration Overview

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

7

Loading...

Loading...