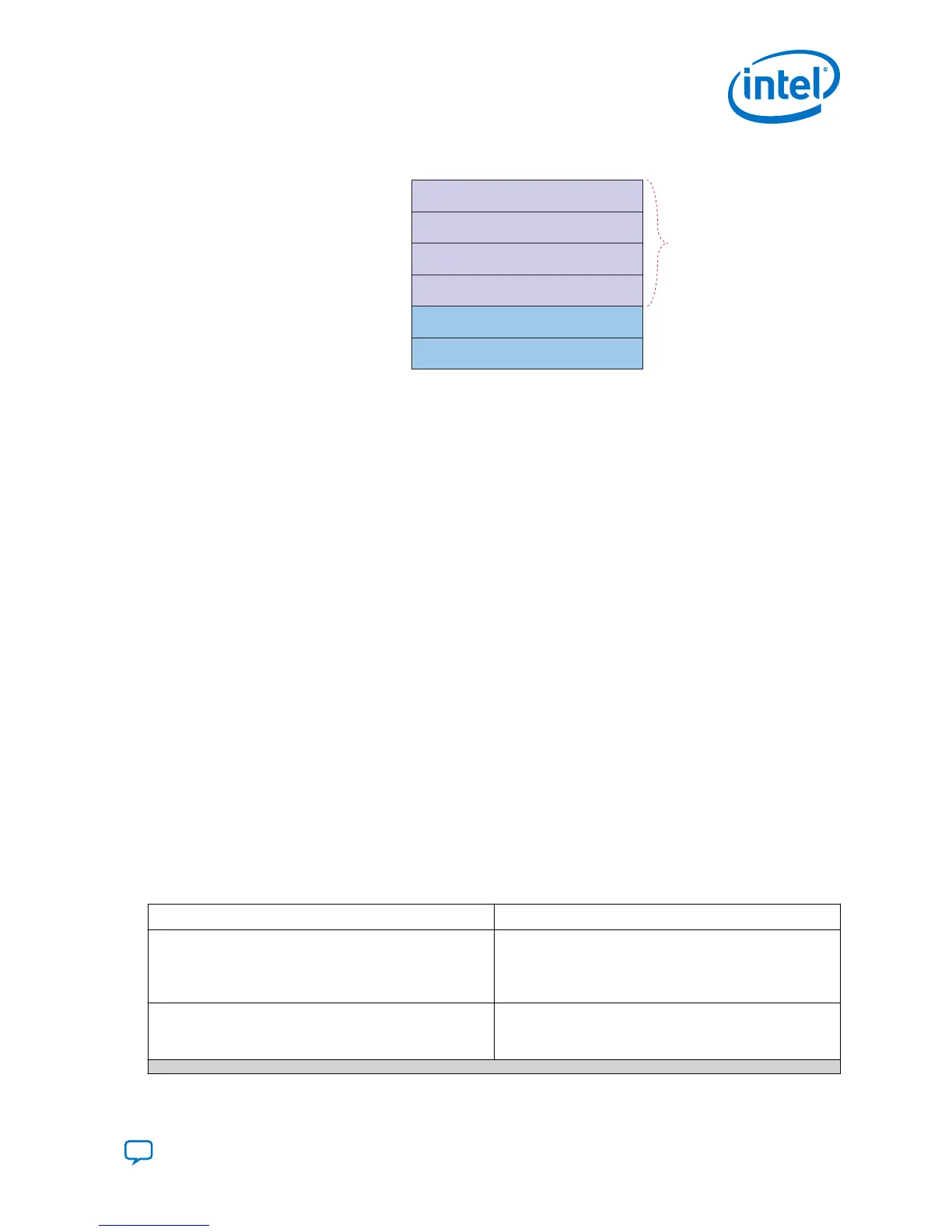

Figure 28. Serial Flash Memory Layout Diagram

Firmware section

is static and

Quartus Prime

version dependent.

32’d256k

Start Address 32’d0

32’d512k

32’d768k

32’d1024k

End Address

(Design dependent)

Dynamic Section (I/O Configuration)

Dynamic Section ( FPGA Core Configuration)

Firmware Section

Firmware Section

Firmware Section

Firmware Section

If you use a third-party programmer to program an .rpd, ensure that the

configuration data is stored starting from address 0 of the serial flash device. If you

use .jic or .pof files, the Intel Stratix 10 Programmer automatically programs the

configuration data starting from address 0 of the serial flash device.

Intel currently support the following third-party flash devices:

• Micron MT25Q 512 megabytes (MB)

• Macronix MX66U 512 MB, 1 and 2 gigabytes (GB)

• Macronix MX25U 128 MB, 256 MB, and 512 MB

• Micron MT25QU 128 MB, 256 MB, 512 MB, 1 GB, and 2 GB

Related Information

Intel Stratix 10 SoC FPGA Bitstream Sections

3.2.6. AS_CLK

The Intel Stratix 10 device drives AS_CLK to the serial flash device. An internal

oscillator or the external clock that drives the OSC_CLK_1 pin generates AS_CLK.

Using an external clock source allows the AS_CLK to run at a higher frequency. If you

provide a 25 MHz, 100 MHz, or 125 MHz clock to the OSC_CLK_1 pin, the AS_CLK can

run up to 133 MHz. Set the maximum required frequency for the AS_CLK pin in the

Intel Quartus Prime software as described in Active Serial Configuration Software

Settings on page 58. The AS_CLK pin runs at or below your selected frequency.

Table 24.

Supported configuration clock source and AS_CLK Frequencies in Intel Stratix

10 Devices

Configuration Clock Source

AS_CLK Frequency (MHz)

Internal oscillator • 115

• 77

• 58

• 25

OSC_CLK_1

• 25

• 50

• 80

continued...

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

57

Loading...

Loading...