Configuration Scheme MSEL[2:0]

AS (Normal mode) 011

SD/MMC x4/x8 100

JTAG only

(3)

111

Related Information

• Intel Stratix 10 GX and SX Device Family Pin Connection Guidelines

• POR Specifications in Intel Stratix 10 Device Datasheet

2.4.3. Device Configuration Pins

All configuration schemes use the same dedicated pins for the standard control signals

shown in Intel Stratix 10 Configuration Timing Diagram on page 14.

There are no dedicated pins for the following signals:

•

PR_REQUEST

•

PR_ERROR

•

PR_DONE

•

CvP_CONFDONE

•

SEU_ERROR

•

DIRECT_TO_FACTORY

You can use the unused SDM I/O pins for CvP_CONFDONE, DIRECT_TO_FACTROY, and

SEU_ERROR pins. You can only use GPIO for PR_REQUEST, PR_ERROR, and PR_DONE

pins by specifying them in the Intel Quartus Prime software and connecting them to

the Partial Reconfiguration External Configuration Controller Intel Stratix 10 FPGA IP.

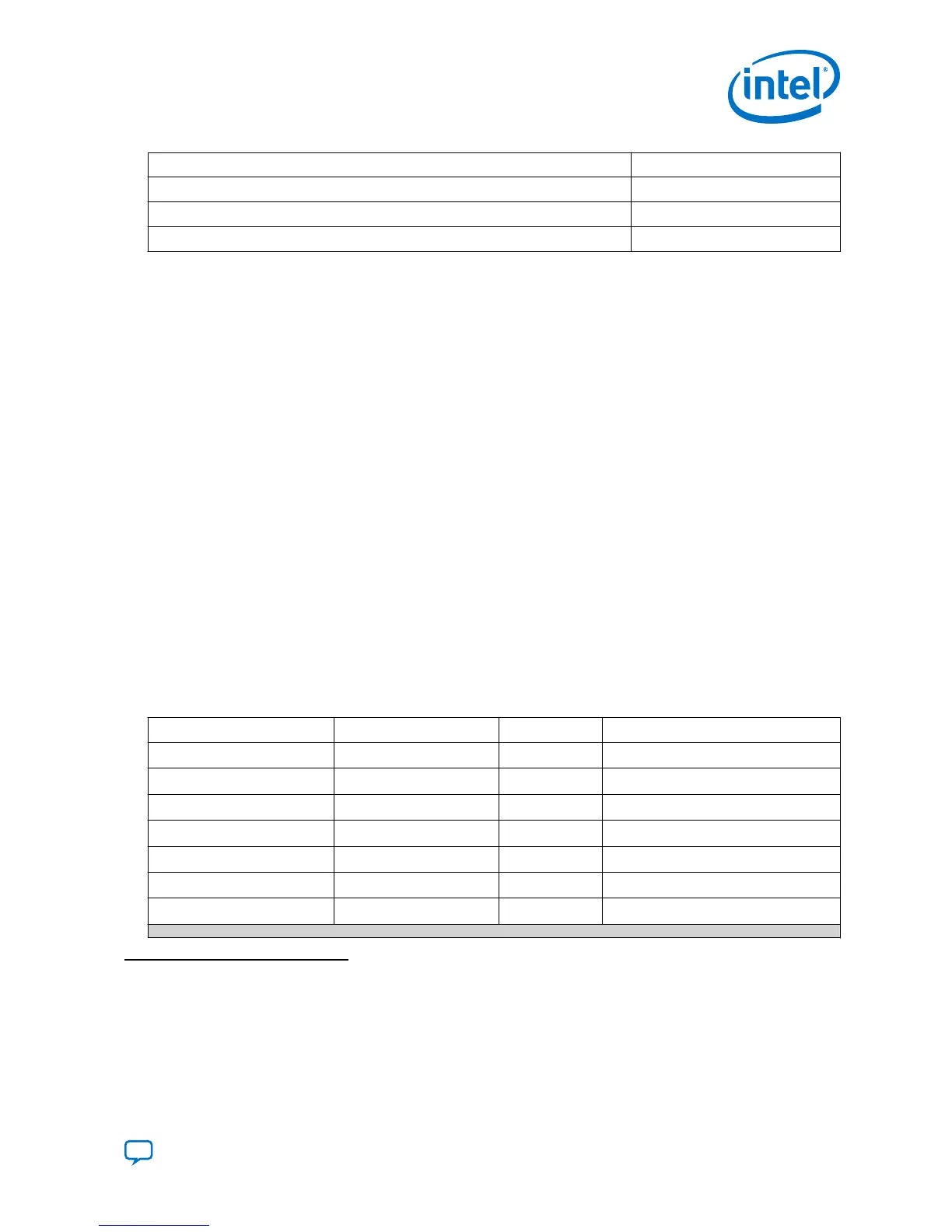

Table 5. Intel Stratix 10 Device Configuration Pins

Configuration Function Configuration Scheme Direction Powered by

TCK

(4)

JTAG Input V

CCIO_SDM

TDI

(4)

JTAG Input V

CCIO_SDM

TMS

(4)

JTAG Input V

CCIO_SDM

TDO

(4)

JTAG Output V

CCIO_SDM

nSTATUS

All schemes Output V

CCIO_SDM

nCONFIG

All schemes Input V

CCIO_SDM

MSEL[2:0]

(5)

All schemes Input V

CCIO_SDM

continued...

(2)

If you use AS Fast mode and are not concerned about 100 ms PCIe linkup, you must still ramp

the VCCIO_SDM supply within 18 ms. This ramp-up requirement ensures that the AS x4 device

is within its operating voltage range when the Intel Stratix 10 device begins to access it.

(3)

JTAG configuration works with any MSEL settings, unless disabled for security.

(4)

The JTAG pins can access the HPS JTAG chain in Intel Stratix 10 SoC devices.

2. Intel Stratix 10 Configuration Details

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

19

Loading...

Loading...