JTAG Configuration

Note: You can perform JTAG configuration anytime from any state except the power-on and

SDM startup state. The Intel Stratix 10 device cancels the previous configuration and

accepts the reconfiguration data from the JTAG interface. The nCONFIG signal must be

held in a stable or low state during JTAG configuration. A falling edge on the nCONFIG

signal cancels the JTAG configuration.

Note:

The SDM only samples the MSEL pins at power-on and initiates bitstream configuration

using the configuration scheme specified at power-on.

Related Information

Booting and Configuration in the Intel Stratix 10 Hard Processor System Technical

Reference Manual

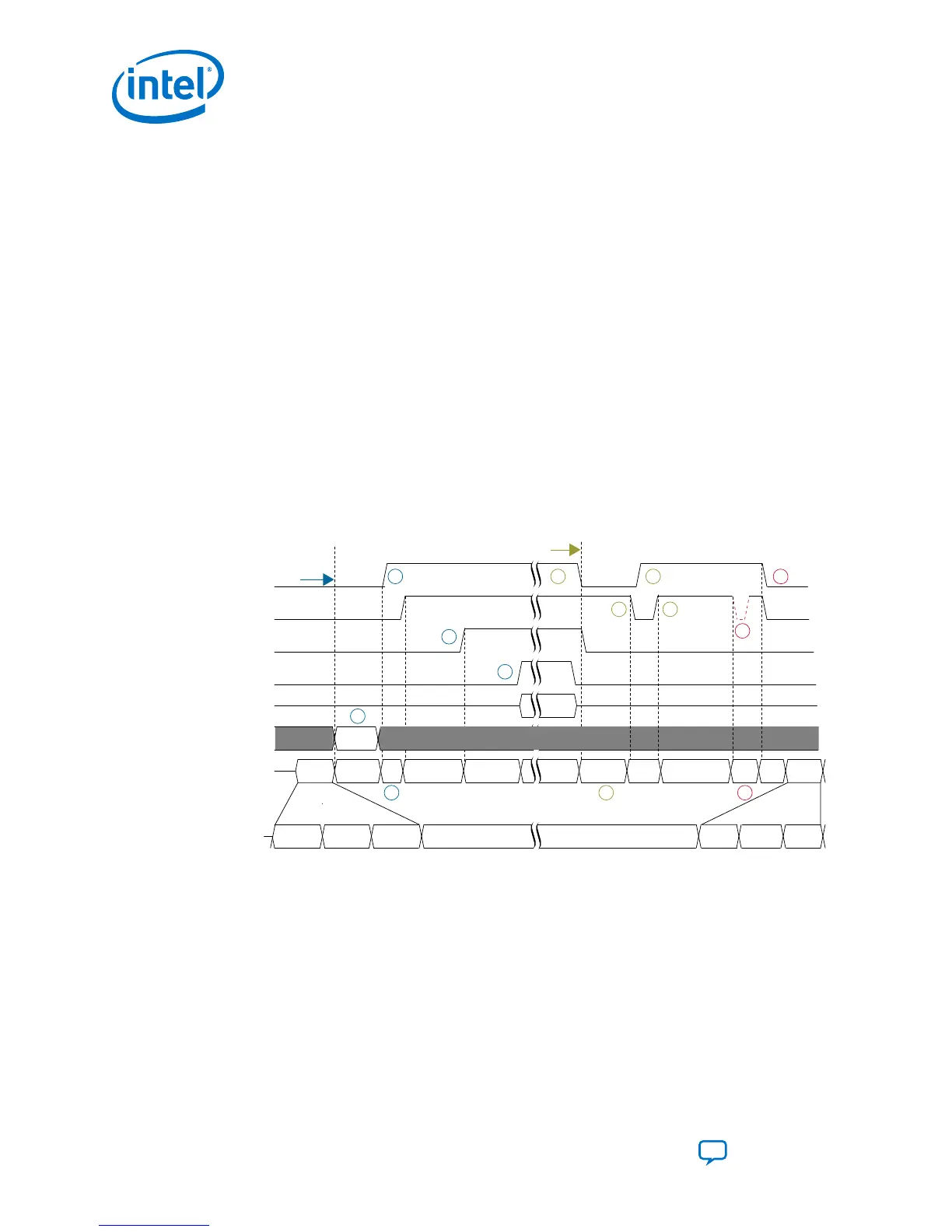

2.2. Intel Stratix 10 Configuration Timing Diagram

The SDM drives Intel Stratix 10 device configuration.

Figure 4. Configuration, Reconfiguration and Error Timing Diagram

nCONFIG

nSTATUS

CONF_DONE

INIT_DONE

User I/Os

MSEL[2:0]

Config

State

Power Supply

Status

Power

-On

SDM

Start

Idle Configuration Initialization

User

Mode

Device

Clean

Idle Configuration IdleError

Power

Down

Group 1

Supply Up

Group 2

Supply Up

Group 3

Supply Up

Group 3

Down

Group 2

Down

Group 1

Down

Power

on Reset

Reconfiguration

triggered

Sample

Initial Configuration Reconfiguration Configuration Error

1

2

3

4

5

1

3

2

4

5

1

2

3

Initial Configuration Timing

The first section of the figure shows the expected timing for initial configuration after a

normal power-on reset. The initial state of the nCONFIG and nSTATUS signals is low.

2. Intel Stratix 10 Configuration Details

UG-S10CONFIG | 2018.11.02

Intel Stratix 10 Configuration User Guide

Send Feedback

14

Loading...

Loading...