3.1.6. IP for Use with the Avalon-ST Configuration Scheme: Intel FPGA

Parallel Flash Loader II IP Core

3.1.6.1. Functional Description

You can either program the CPLD and the flash memory concurrently or separately.

You can use the Parallel Flash Loader II Intel FPGA IP core (PFL II) with an external

host, such as the MAX II, MAX V, or Intel MAX 10 devices to complete the following

tasks:

• Program configuration data into a flash memory device using JTAG interface.

• Configure the Intel Stratix 10 device with the Avalon-ST configuration scheme

from the flash memory device.

3.1.6.1.1. Programming CFI Flash

You can program the CFI flash using the PFL II IP core via the JTAG interface. Before

you can program the CFI flash with configuration data, you must program the PFL II

IP core into the host. You can only program with a .pof file and only use the Intel

Quartus Prime Programmer to program the flash.

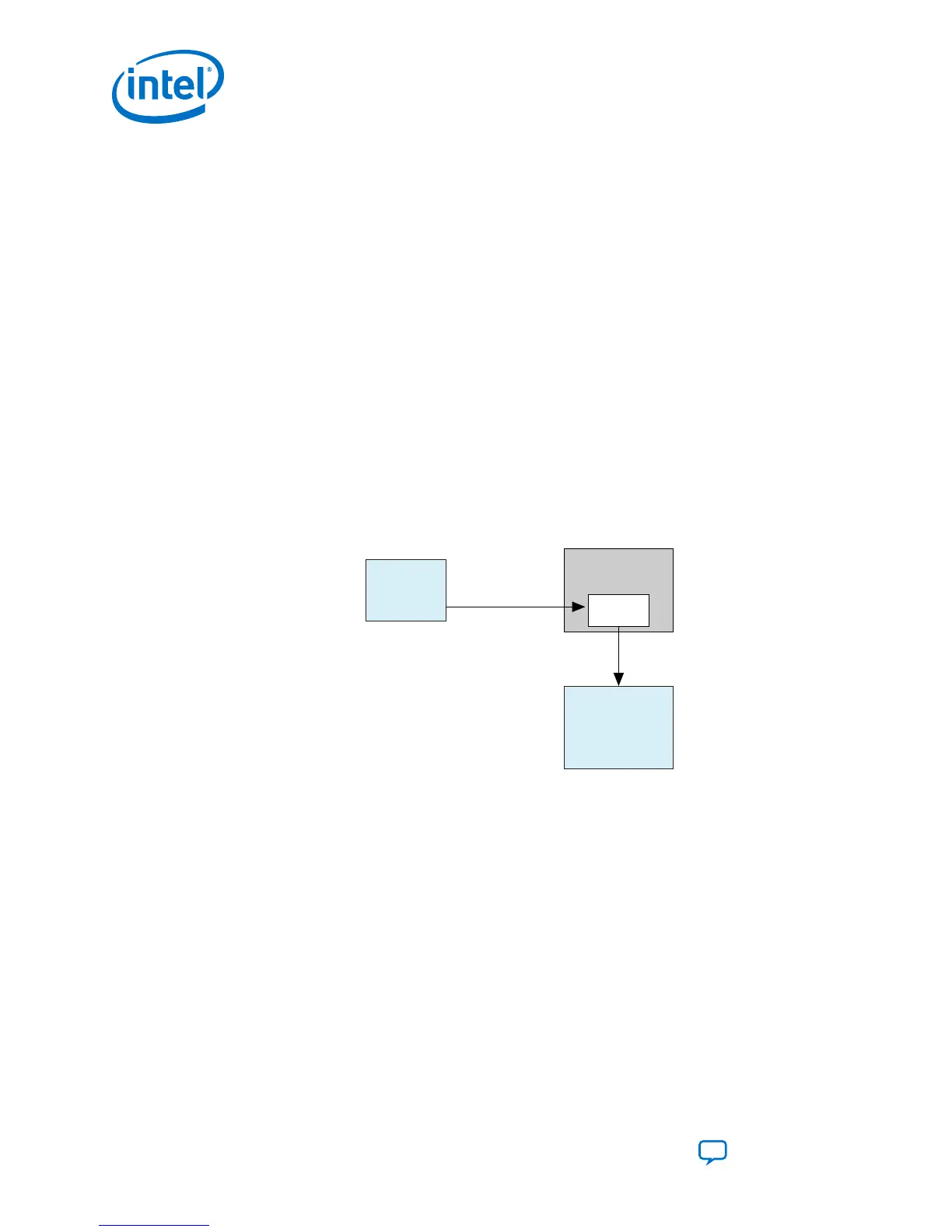

Figure 11. Programming the CFI Flash Memory with the JTAG Interface

External

Host

CFI Flash

Memory

Configuration Data

Common

Flash

Interface

PFL II

Quartus Prime

Software

using JTAG

The PFL II IP core supports dual P30 or P33 CFI flash memory devices in burst read

mode to achieve faster configuration times. You can connect two identical P30 or P33

CFI flash memory devices to the host in parallel using the same data bus, clock, and

control signals. During FPGA configuration, the AVST_CLK frequency is four times

faster than the flash_clk frequency.

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Intel Stratix 10 Configuration User Guide

Send Feedback

34

Loading...

Loading...