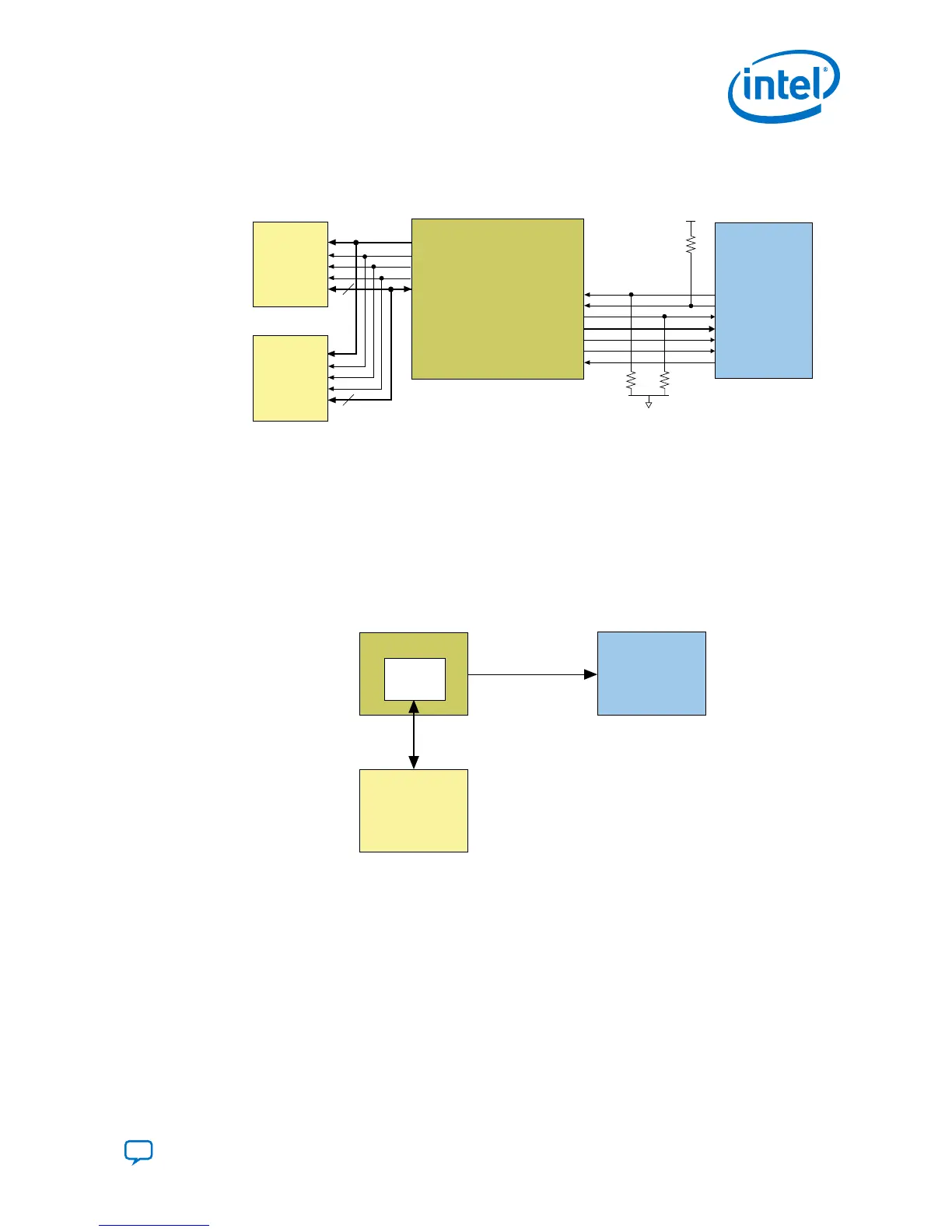

Figure 12. PFL II IP core with Dual P30 or P33 CFI Flash Memory Devices

The flash memory devices in the dual P30 or P33 CFI flash solution must have the same memory density from

the same device family and manufacturer.

V

CC

P30/P33 CFI Flash

External Host with PFL II IP Core

Intel Stratix 10

P30/P33 CFI Flash

16

16

10k

Ω

10kΩ

10kΩ

ADDR[24..0]

NCE

NWE

NOE

DATA[15..0]

ADDR[24..0]

NCE

NWE

NOE

DATA[15..0]

flash_addr[24..0]

flash_nce

flash_nwe

flash_noe

flash_data[31..0]

fpga_conf_done

fpga_nstatus

fpga_nconfig

avst_data

avst_clk

CONF_DONE

nSTATUS

nCONFIG

AVSTx8_DATA/AVST_DATA

AVSTx8_CLK/AVST_CLK

avst_valid

avst_ready

AVSTx8_VALID/AVST_VALID

AVST_READY

Related Information

Intel Stratix 10 GX FPGA Development Kit

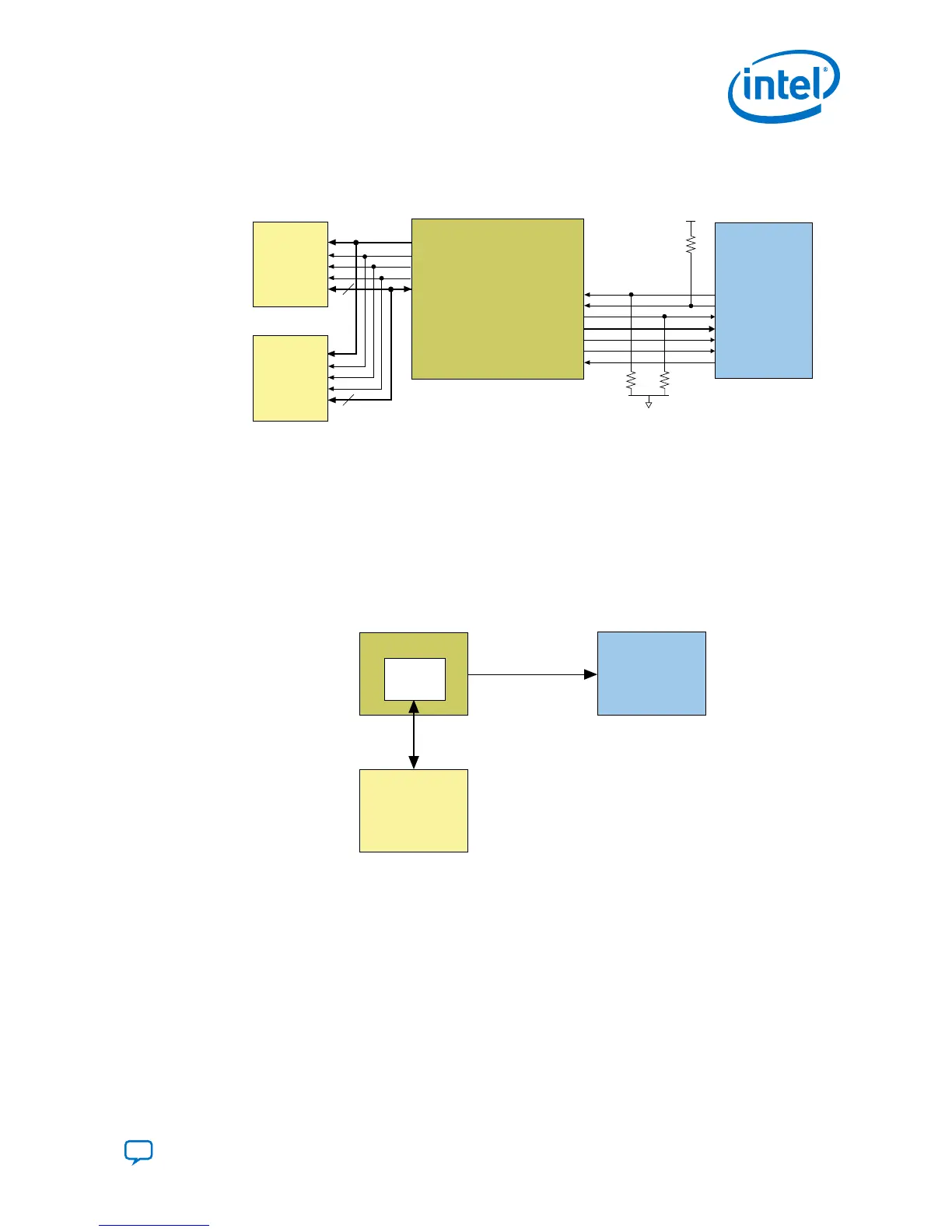

3.1.6.1.2. Controlling Avalon-ST Configuration with PFL II IP Core

The PFL II IP core in the host determines when to start the configuration process, read

the data from the flash memory device, and configure the Intel Stratix 10 using the

Avalon-ST configuration scheme.

Figure 13. FPGA Configuration with Flash Memory Data

Host

Flash

Memory

Intel Stratix 10

Flash

Interface

PFL II

Avalon-ST

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

35

Loading...

Loading...