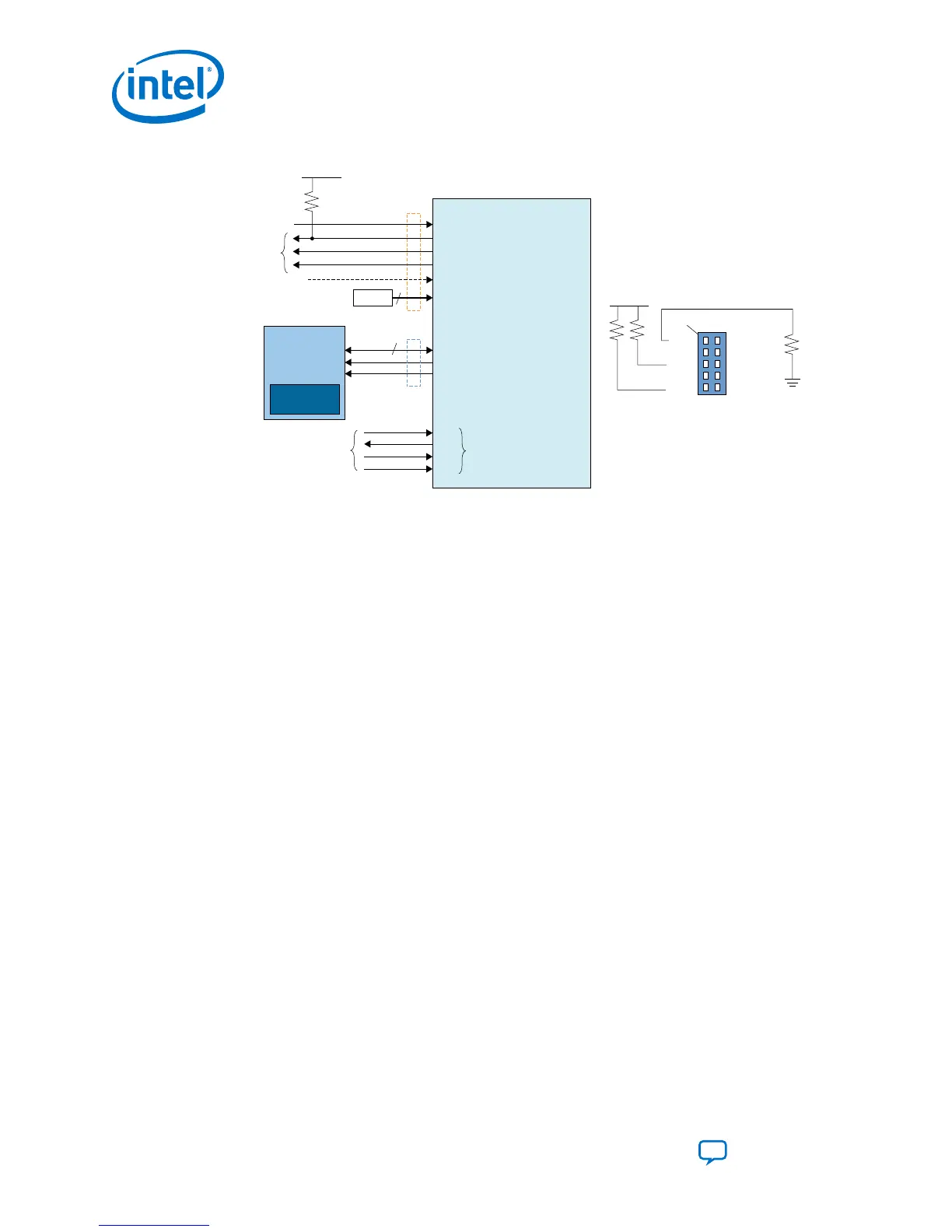

Figure 21. Connections for AS x4 Single-Device Configuration

Pin 1

R

UP

R

DN

R

UP

TCK

TDO

TMS

OPEN

TDI

GND

VCCIO_SDM

OPEN

OPEN

GND

G

ND

V

CCIO_SDM

Intel® Stratix®10

nCONFIG

nSTATUS

CONF_DONE

INIT_DONE

OSC_CLK_1

MSEL[2:0]

AS_DATA[3:0]

AS x4 Flash Memory

AS_CLK

AS_nCS0

Download cable 10 pin male header (JTAG mode)

DATA[3:0]

DCLK

nCS0

Configuration

Control Signals

Optional

Monitoring

10kΩ

Optional

Configuration

Data Signals

To JTAG

Header or

JTAG Chain

MSEL

V

CCIO_SDM

3

4

TCK

TDO

TDI

TMS

JTAG

Configuration

Pins

FPGA

Image (.jic)

3M Part number : 2510-6002UB

Related Information

• MSEL Settings on page 18

• Intel Stratix 10 Device Family Pin Connection Guidelines

3.2.2. AS Using Multiple Serial Flash Devices

Intel Stratix 10 devices support one AS x4 flash memory device for AS configuration

and up to three AS x4 flash memories for use with HPS data storage. The MSEL pins

are dual-purpose and operate as MSEL only during POR state. After the FPGA device

enters user mode, you can repurpose the MSEL pins as chip select pins. You must to

ensure appropriate pin chip select pin connections to the configuration AS x4 flash

memory and HPS AS x4 flash memory. Each flash device has a dedicated AS_nCSO pin

but shares other pins.

Refer to the Intel Stratix 10 Device Family Pin Connection Guidelines for additional

information about individual pin usage and requirements.

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Intel Stratix 10 Configuration User Guide

Send Feedback

52

Loading...

Loading...