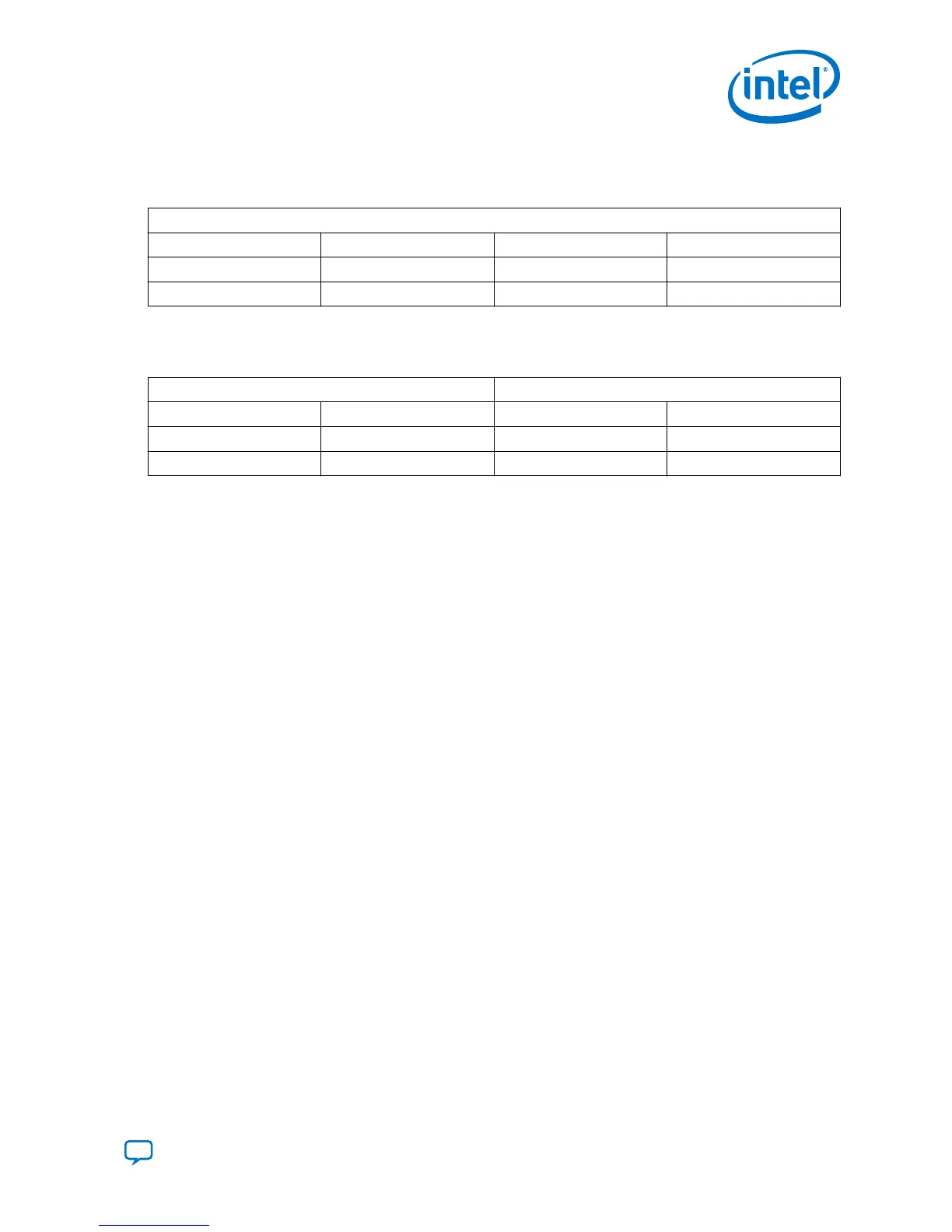

Table 10. Writing 32-bit Data

For a x32 data bus , the first byte in the file is the least significant byte of the configuration double word, and

the fourth byte is the most significant byte.

Double Word = 01EE1B02

LSB: BYTE0 = 02 BYTE1 = 1B BYTE2 = EE MSB: BYTE3 = 01

D[7:0] D[15:8] D[23:16] D[31:24]

0000 0010 0001 1011 1110 1110 0000 0001

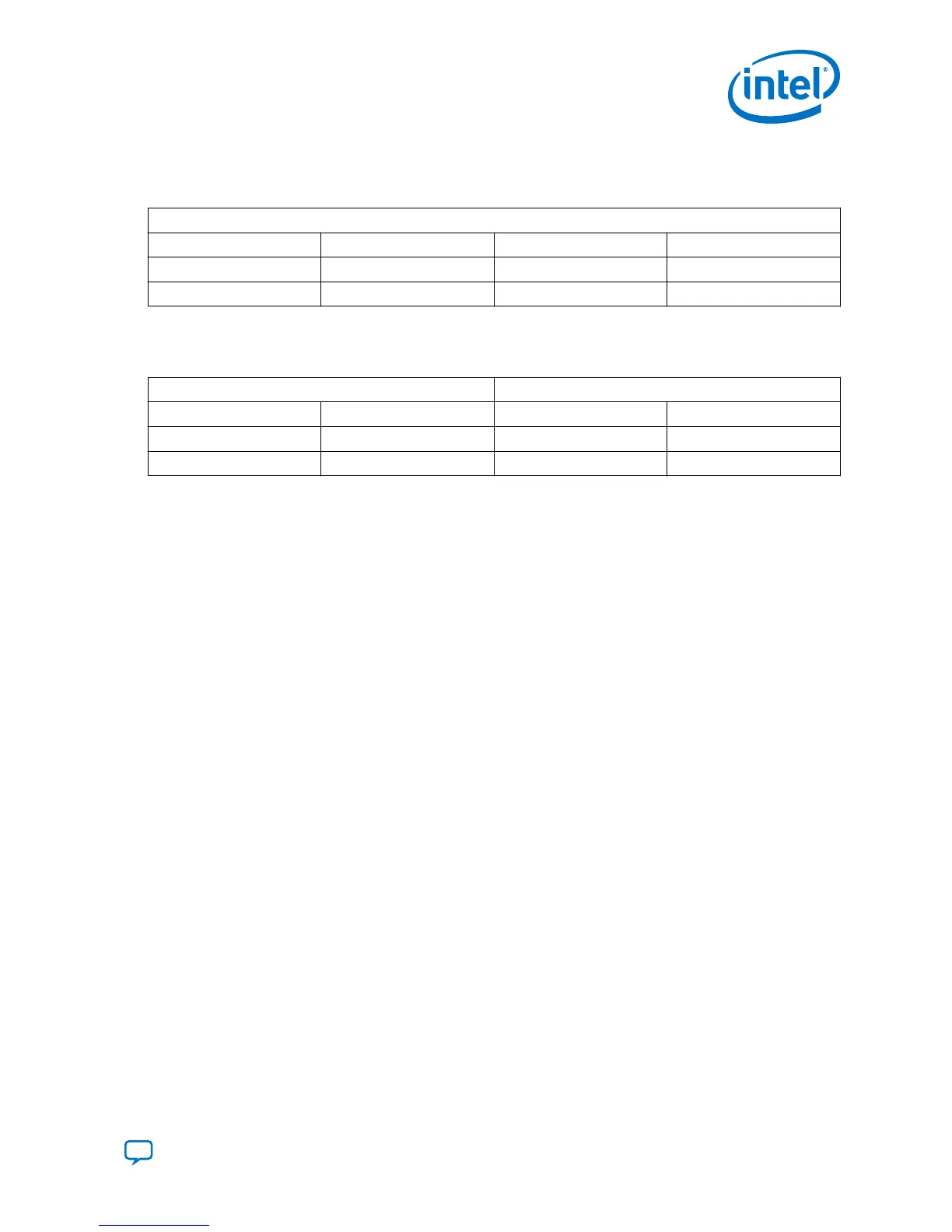

Table 11. Writing 16-bit Data

For a x16 data bus, the first byte in the file is the least significant byte of the configuration word, and the

second byte is the most significant byte of the configuration word.

WORD0 = 1B02 WORD1 = 01EE

LSB: BYTE0 = 02 MSB: BYTE1 = 1B LSB: BYTE2 = EE MSB: BYTE3 = 01

D[7:0] D[15:8] D[7:0] D[15:8]

0000 0010 0001 1011 1110 1110 0000 0001

3.1.5. Debugging Guidelines for the Avalon-ST Configuration Scheme

the Avalon-ST configuration scheme replaces the previously available FPP modes. This

configuration scheme retains similar functionality and performance. Here are the

important differences:

• The Avalon-ST configuration scheme requires you to monitor the flow control

signal, AVST_READY. The AVST_READY signal indicates if the device can receive

configuration data.

•

The AVST_CLK and AVSTx8_CLK clock signals cannot pauses when configuration

data is not being transferred. Data is not transferred when AVST_READY and

AVST_VALID are low. The AVST_CLK and AVSTx8_CLK clock signals must run

continuously until CONF_DONE asserts.

Debugging Suggestions

Here are some debugging tips:

•

Only assert AVST_VALID any time after AVST_READY asserts.

•

Only assert AVST_VALID when the data is valid.

•

Ensure that the AVST_CLK clock signal are continuous until CONF_DONE asserts.

•

If using x8 mode, ensure that you use the dedicated SDM_IO pins for this

interface (clock, data, valid and ready).

• If using x16 or x32 mode, power the IO bank containing the x16 or x32 pins (3A)

at 1.8V.

• Ensure you select the appropriate Avalon-ST configuration scheme in your Intel

Quartus Prime Pro Edition project.

•

Ensure the MSEL pins reflect this mode.

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

33

Loading...

Loading...