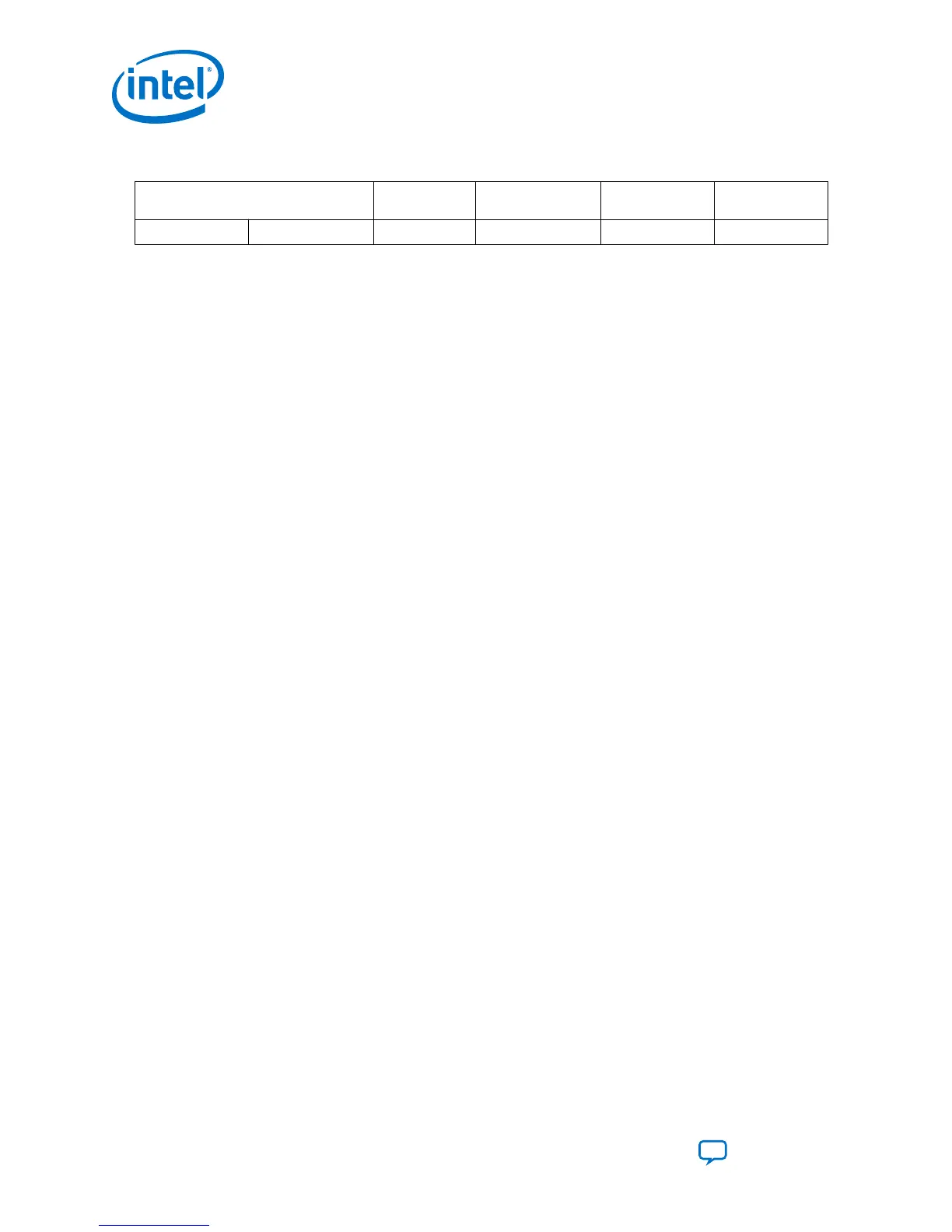

Table 26. Intel Stratix 10 Configuration Data Width, Clock Rates, and Data Rates

Mode Data Width

(bits)

Max Clock Rate Max Data Rate MSEL[2:0]

Passive JTAG 1 30 MHz 30 Mbps 3'b111

Related Information

• Programming Support for Jam STAPL Language

• JTAG Configuration Timing in Intel Stratix 10 Devices

3.4.1. JTAG Single-Device Configuration

To configure a single device in a JTAG chain, the programming software sets the other

devices to bypass mode. A device in bypass mode transfers the programming data

from the TDI pin to the TDO pin through a single bypass register. The configuration

data is available on the TDO pin one clock cycle later.

You can configure the Intel Stratix 10 device through JTAG using a download cable or

a microprocessor.

3.4.1.1. JTAG Single-Device Configuration using Download Cable Connections

Refer to the Intel Stratix 10 Device Family Pin Connection Guidelines for additional

information about individual pin usage and requirements.

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Intel Stratix 10 Configuration User Guide

Send Feedback

64

Loading...

Loading...