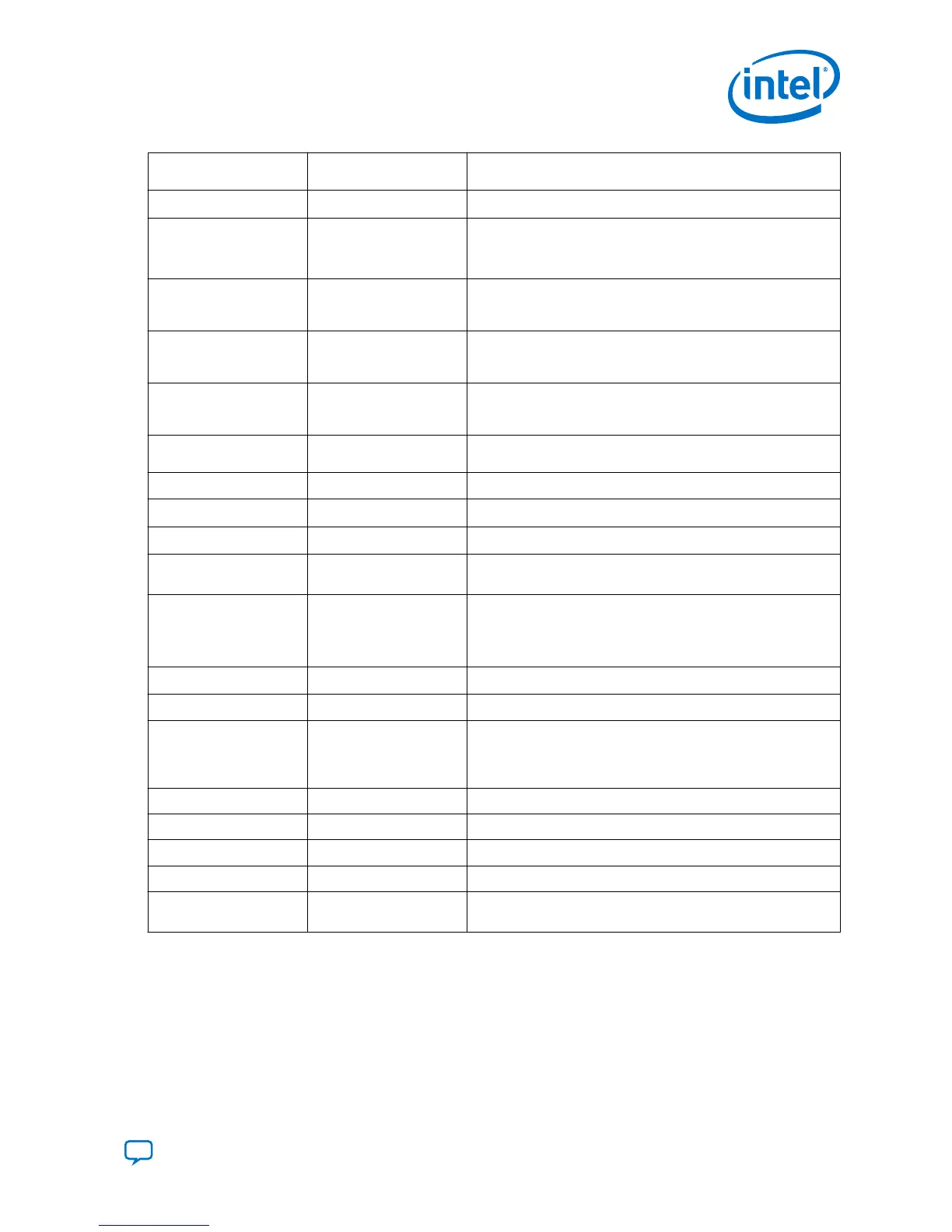

Configuration Pin Names

(Pre-Intel Stratix 10)

Intel Stratix 10 Pin

Names

Notes

DEV_CLRn

Not Available

INIT_DONE

SDM_IO0

SDM_IO16

INIT_DONE

No longer Open Drain.

MSEL[0] SDM_IO5 (MSEL[0]) After the SDM samples MSEL this pin functions as per the

configuration mode selected. Do not connect directly to power.

Use 4.7 KΩ pull-up or pull-downs, as appropriate.

MSEL[1] SDM_IO7 (MSEL[1]) After the SDM samples MSEL, this pin functions as per the

configuration mode selected. Do not connect directly to power.

Use 4.7 KΩ pull-up or pull-downs, as appropriate.

MSEL[2] SDM_IO9 (MSEL[2]) After the SDM samples MSEL, this pin functions as per the

configuration mode selected. Do not connect directly to power.

Use 4.7 KΩ pull-up or pull-downs, as appropriate.

NSTATUS nSTATUS

No longer Open Drain. Intel recommends a 10 KΩ pull-up to

V

CCIO_SDM

.

NCE

Not Available Multi-device configuration is not supported.

NCEO

Not Available

Multi-device configuration is not supported.

DATA[31:0] (PP32/PP16) AVST_DATA[31:0]

Avalon-ST x8 uses SDM pins for data pins.

DATA[7:0] (PP8) SDM _IO pins

(AVSTx8_DATAn)

nCSO[2:0] SDMIO_8 (AS_nCSO3)

SDMI_O7 (AS_nCSO2)

SDMI_O9 (AS_nCSO1)

SDM_IO5 (AS_nCSO0)

Intel Stratix 10 supports up to 4 cascaded AS devices

nIO_PULLUP

Not Available

Use a JTAG instruction to invoke.

AS_DATA0_ASDO SDM_IO4 (AS_DATA0)

AS_DATA[3:1]

SDM_IO6 (AS_DATA3)

SDM_IO3 (AS_DATA2)

SDM_IO1 (AS_DATA1)

Unlike earlier device families, the AS interface does not

automatically tristate at power-on. When you set MSEL to JTAG,

the SDM drives the AS_CLK, AS_DATA0-AS_DATA3, and

AS_CS0-AS_CS3, MSEL pins until POR.

PR_REQUEST GPIO*

No dedicated location.

PR_READY GPIO*

No dedicated location.

PR_ERROR

GPIO* No dedicated location.

PR_DONE GPIO*

No dedicated location.

CVP_CONFDONE Any unused SDM_IO

CVP_CONFDONE

Related Information

Setting Configuration Clock Source on page 23

6. Intel Stratix 10 Debugging Guide

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

99

Loading...

Loading...