68 TOS5300

Interlock Feature

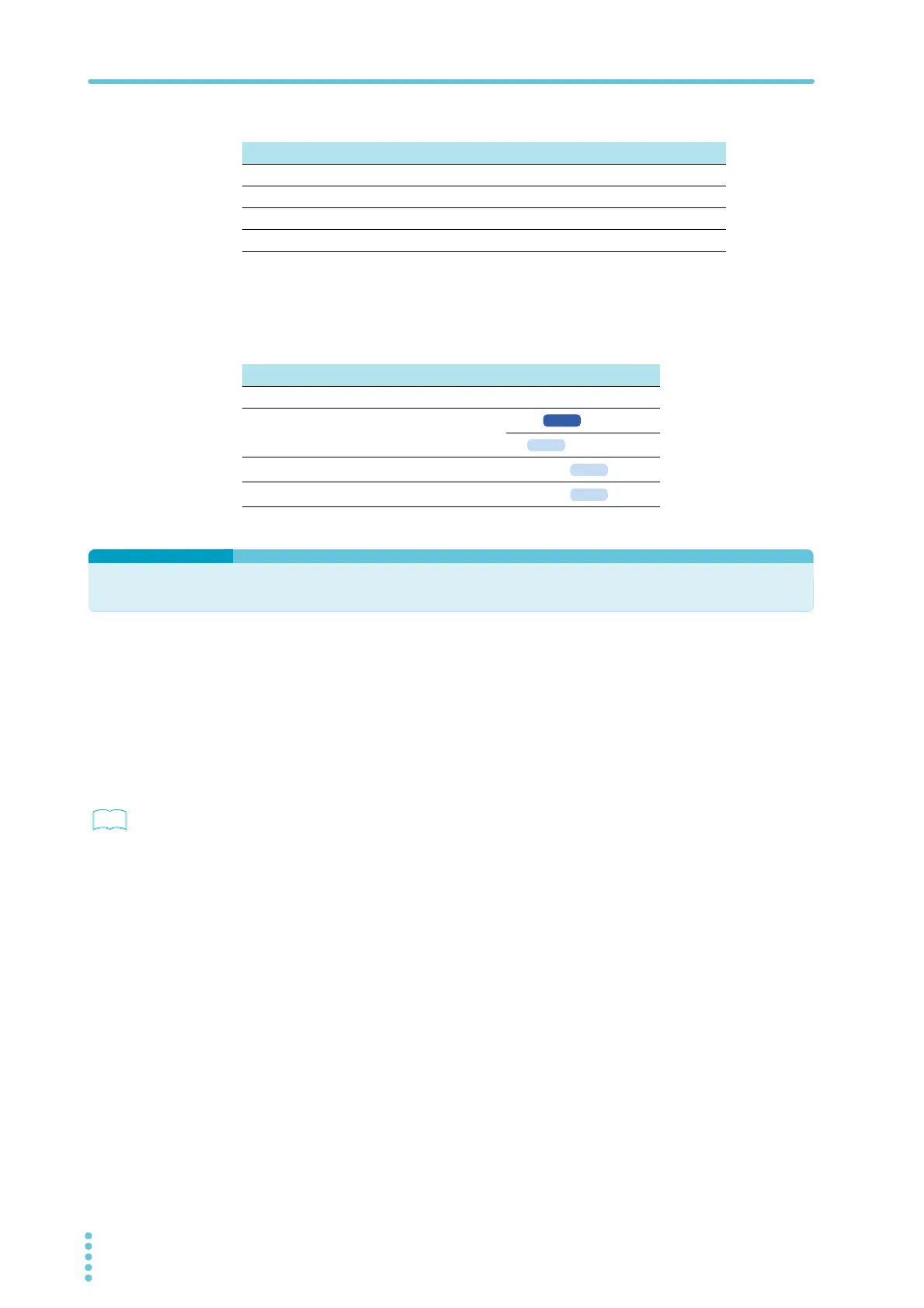

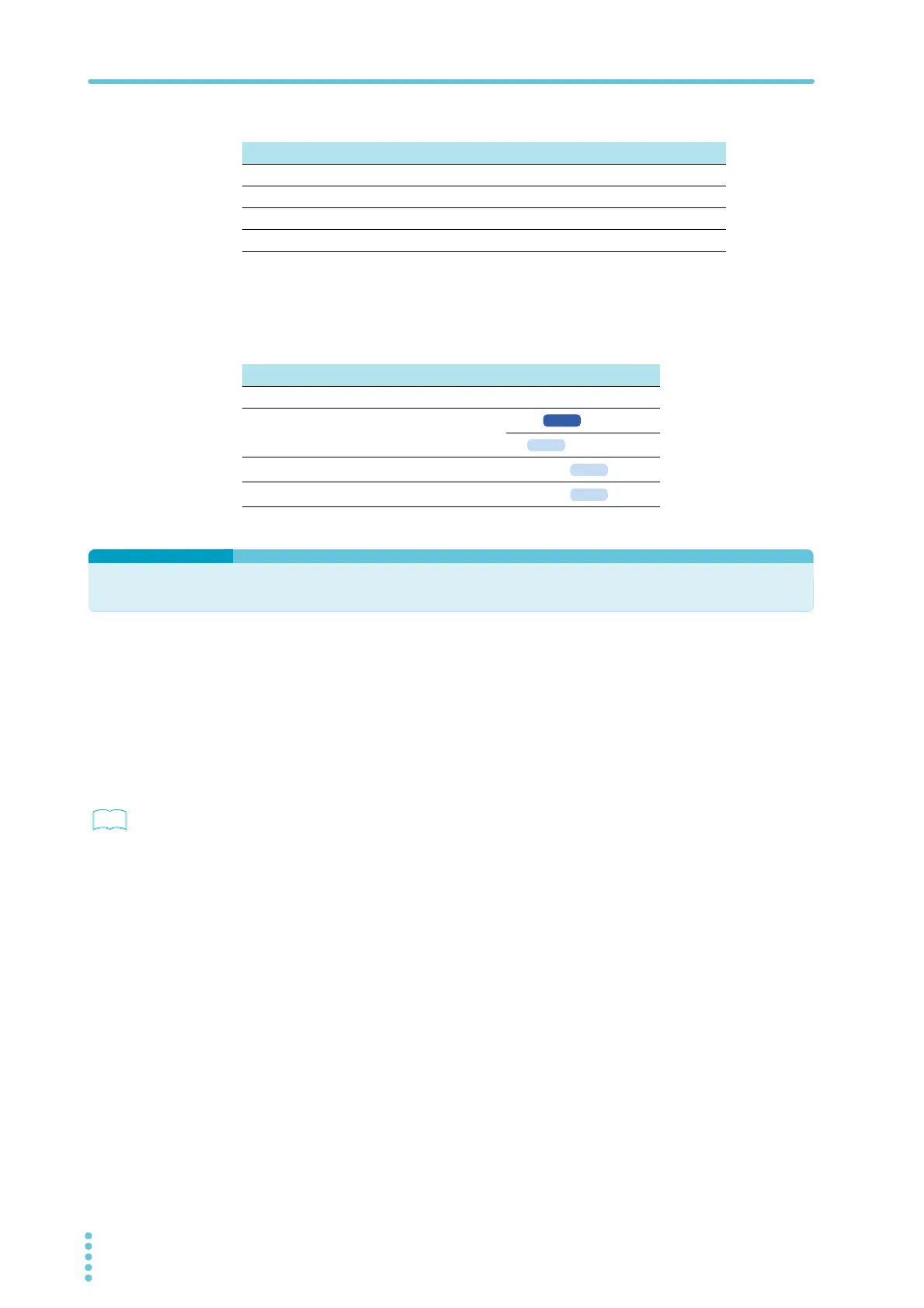

Selecting the test mode

The relationship between the PM0, PM1, TEST SEL, and AUTO SEL signals and the test mode that is

recalled is shown in the table below.

Interlock Feature

This feature links the TOS5300 Series to an external device to stop output appropriately. This

ensures the safety of the operator.

While the interlock feature is active, even if you press the START switch or apply a start signal from

an external controller, the TOS5300 Series will not perform testing. While the interlock signal is

being applied, you cannot release PROTECTION mode by pressing the STOP switch or applying a

stop signal.

By using the interlock feature, you can control the TOS5300 Series output from an external source.

This ensures safe operation of the tester.

p.23

The first time that you turn the POWER switch on after you purchase the TOS5300 Series, the tester

will be in PROTECTION mode through the interlock feature. You can use the included SIGNAL I/O

plug to easily release the PROTECTION mode.

Attaching the included SIGNAL I/O plug connects pin numbers 1 and 13, the INTERLOCK+ and

INTERLOCK- pins. Only use this plug to easily release the PROTECTION mode.

When you are actually performing tests, use the interlock feature to ensure safety.

During withstanding voltage and insulation resistance tests in which you are using tools, (1) placing

a cover over the DUT so that output is turned off whenever the cover is removed to prevent electric

shock and (2) placing a safety fence around the work area where withstanding voltage and

insulation resistance tests are being performed so that output is turned off whenever the fence is

opened are both examples of effective safety measures.

■ Interlock signal input conditions

Open across terminals

• When the resistance across the positive and negative terminals is 1.2 kΩ or greater.

• If you are using transistors or an optical device, when the current across the positive and

negative terminals is 5 mA or less.

PM0 PM1 TEST SEL AUTO SEL Recalled panel memory number

H H L L memory 1

L H L L memory 2

H L L L memory 3

L L L L Enables TEST SEL and AUTO SEL

PM0 PM1 TEST SEL AUTO SEL Recalled test mode

LLLLACW

LLHL

DCW

IR

LLHH

IR → ACW

LLLH

ACW → IR

Loading...

Loading...