MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

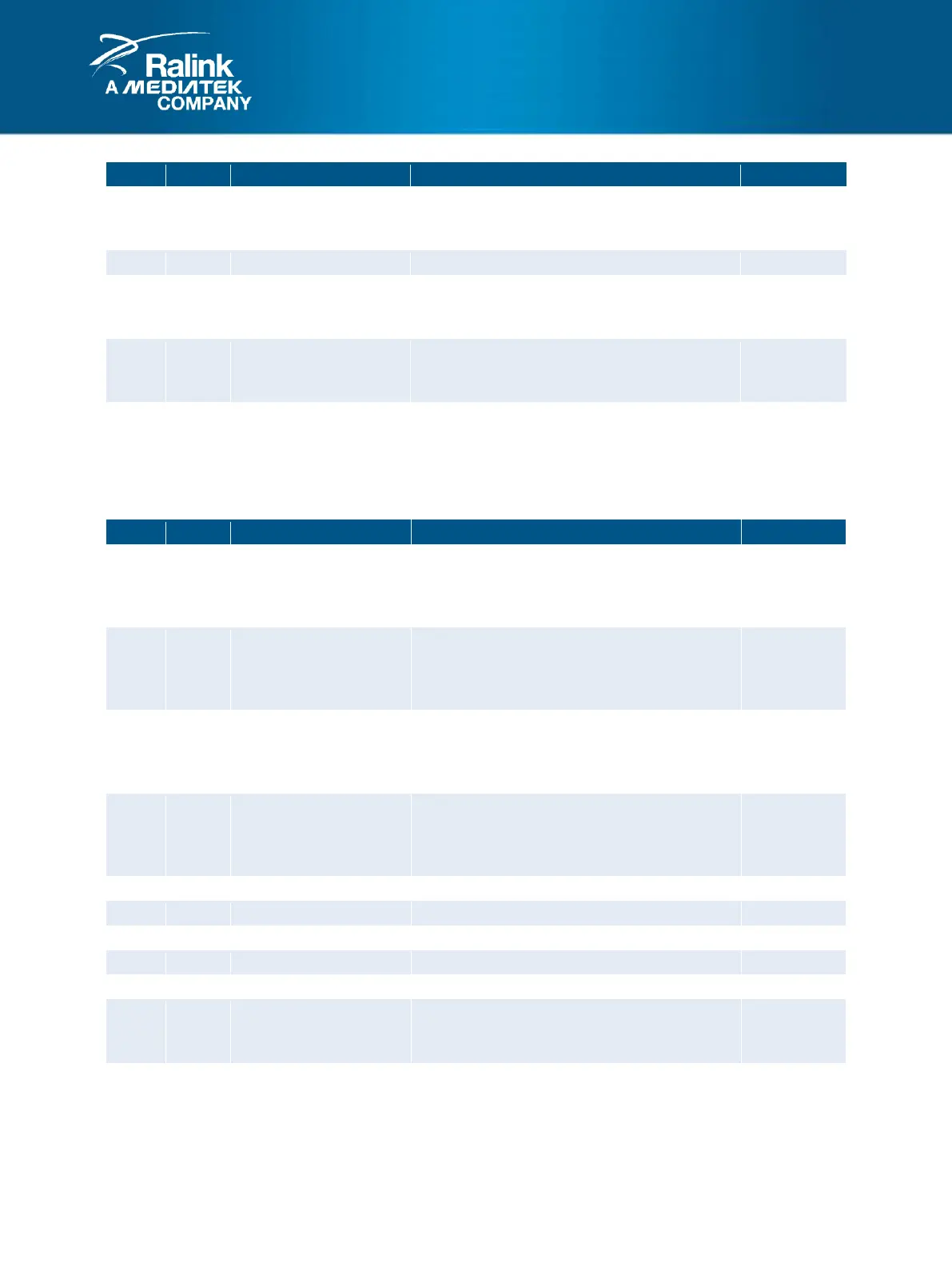

Rx Queue 0 Done Interrupt

Asserts when an Rx packet is received on

Queue 0.

Tx Queue 1 Done Interrupt

Asserts when a Tx Queue 1 packet is

transmitted.

Tx Queue 0 Done Interrupt

Asserts when a Tx Queue 0 packet is

transmitted.

NOTE:

Read:

0: Interrupt not asserted.

1: Interrupt asserted

Write

1: Clear the interrupt

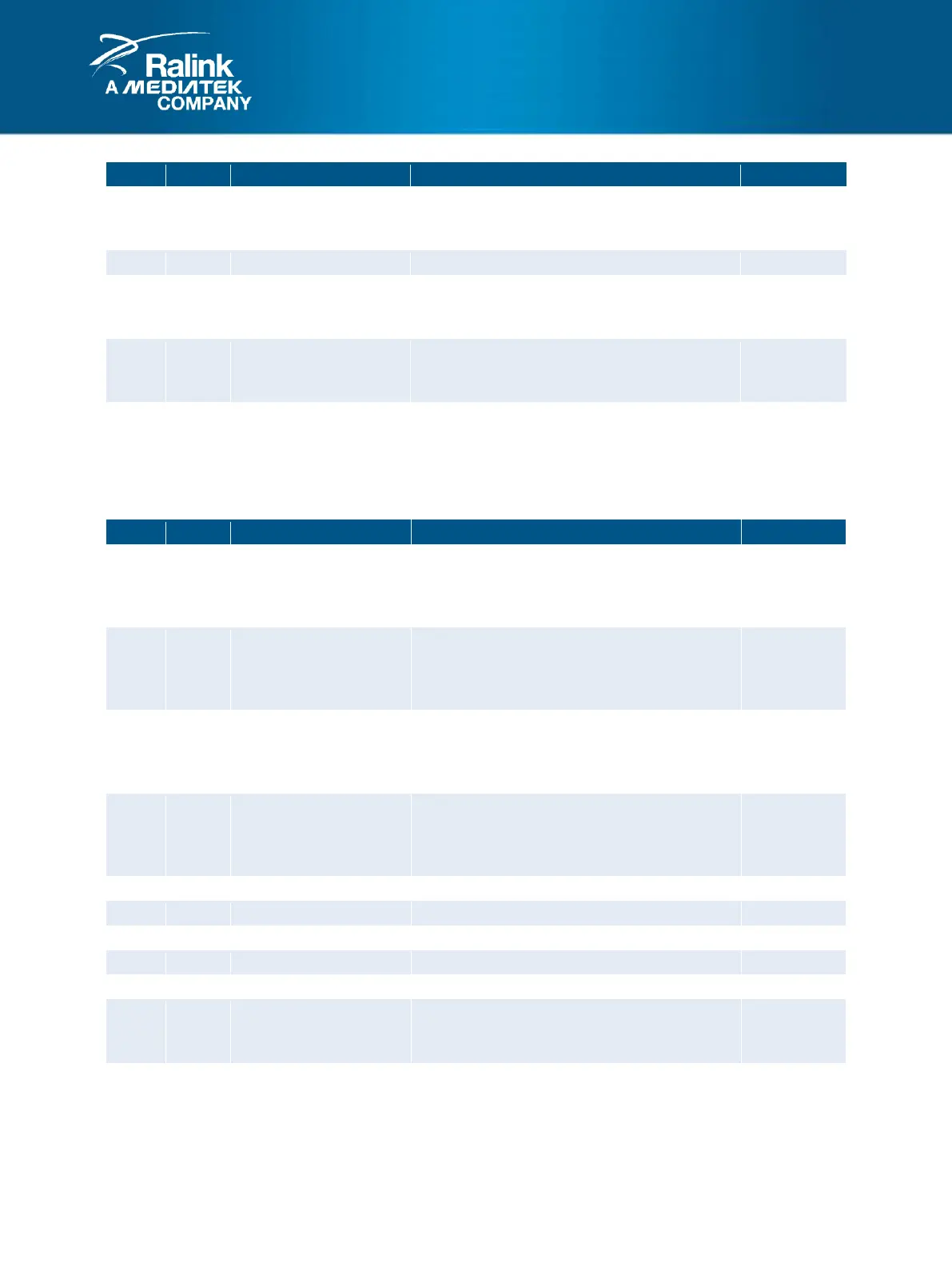

240. INT_MASK: (offset: 0x1228)

Masks the Rx Coherent interrupt. This interrupt

asserts when the Rx DMA is ready to handle a

queue, but cannot access the queue because

the driver is not ready.

Masks the Rx Delay interrupt. This interrupt

asserts when the number of pending Rx

interrupts has reached a specified level, or

when the pending time is reached.

Masks the Tx Coherent interrupt. This interrupt

asserts when the Tx DMA is ready to handle a

queue, but cannot access the queue because

the driver is not ready.

Masks the Tx Delay interrupt. This interrupt

asserts when the number of pending Tx

interrupts has reached a specified level, or

when the pending time is reached.

MCU command interrupt 3 enable: Reserved

MCU command interrupt 2 enable: Reserved

MCU command interrupt 1 enable: Reserved

MCU command interrupt 0 enable: Reserved

Masks the Rx Queue 1 Done interrupt. This

interrupt asserts when an Rx packet is received

on Queue 1.

Masks the Rx Queue 0 Done interrupt. This

interrupt asserts when an Rx packet is received

on Queue 0.

Loading...

Loading...