MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

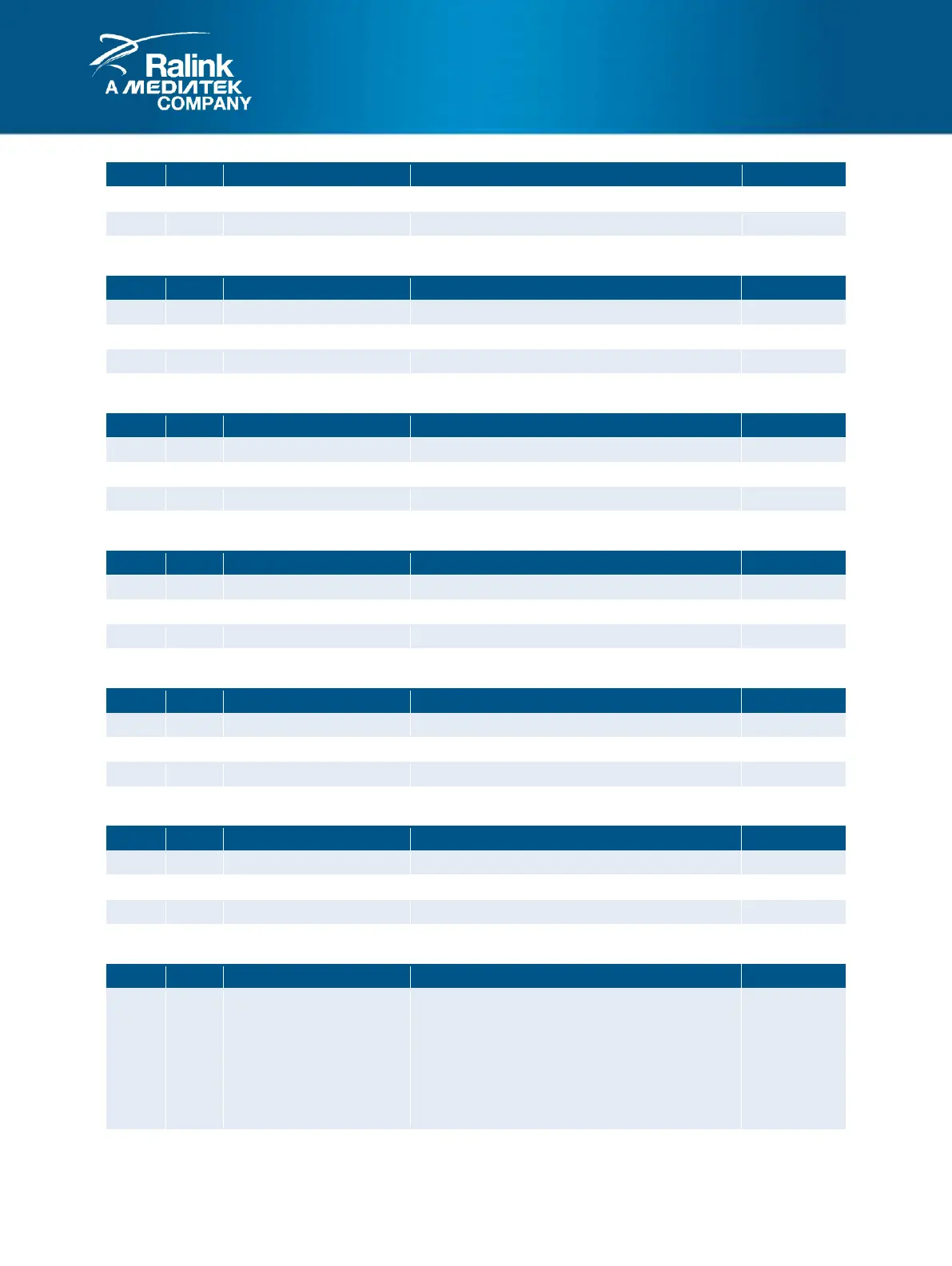

VLAN Identifier for VLAN Table Index 5

VLAN Identifier for VLAN Table Index 4

333. VTIM4: VID to Table Index Map 4 Register (offset: 0x010C)

VLAN Identifier for VLAN Table Index 7

VLAN Identifier for VLAN Table Index 6

334. VTIM5: VID to Table Index Map 5 Register (offset: 0x0110)

VLAN Identifier for VLAN Table Index 9

VLAN Identifier for VLAN Table Index 8

335. VTIM6: VID to Table Index Map 6 Register (offset: 0x0114)

VLAN Identifier for VLAN Table Index 11

VLAN Identifier for VLAN Table Index 10

336. VTIM7: VID to Table Index Map 7 Register (offset: 0x0118)

VLAN Identifier for VLAN Table Index 13

VLAN Identifier for VLAN Table Index 12

337. VTIM8: VID to Table Index Map 8 Register (offset: 0x011C)

VLAN Identifier for VLAN Table Index 15

VLAN Identifier for VLAN Table Index 14

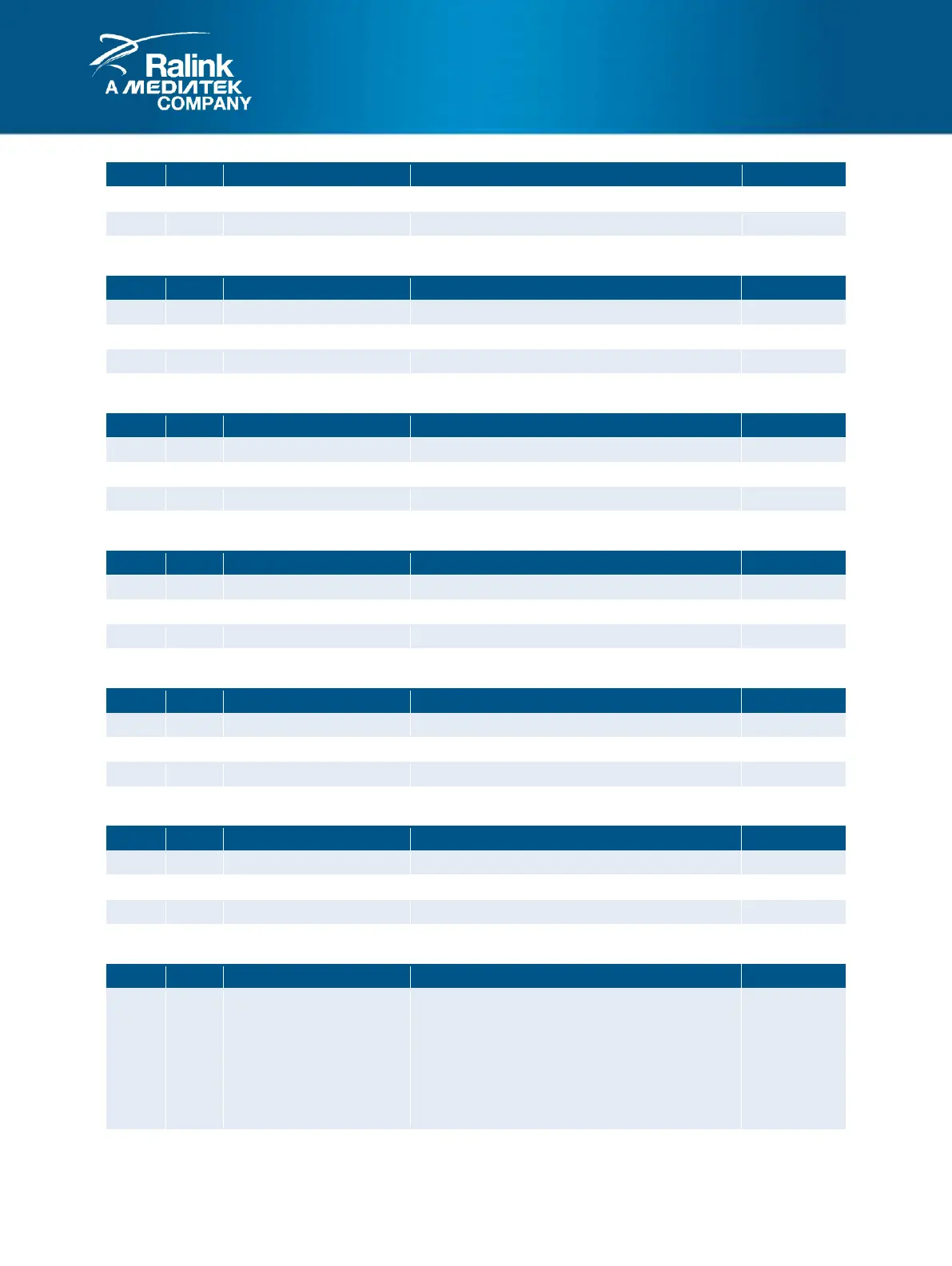

338. DBGC: Debug Control Register (offset: 0x0200)

Debug Mode Is Busy

SW can set this bit to 1 only if this bit is reset.

After DBGD1 and DBGD2 registers have been

written and this bit is set, this chip will perform

debug commands on the corresponding debug

control and data which reside in different

blocks based on DEBUG_ID.

Loading...

Loading...