MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

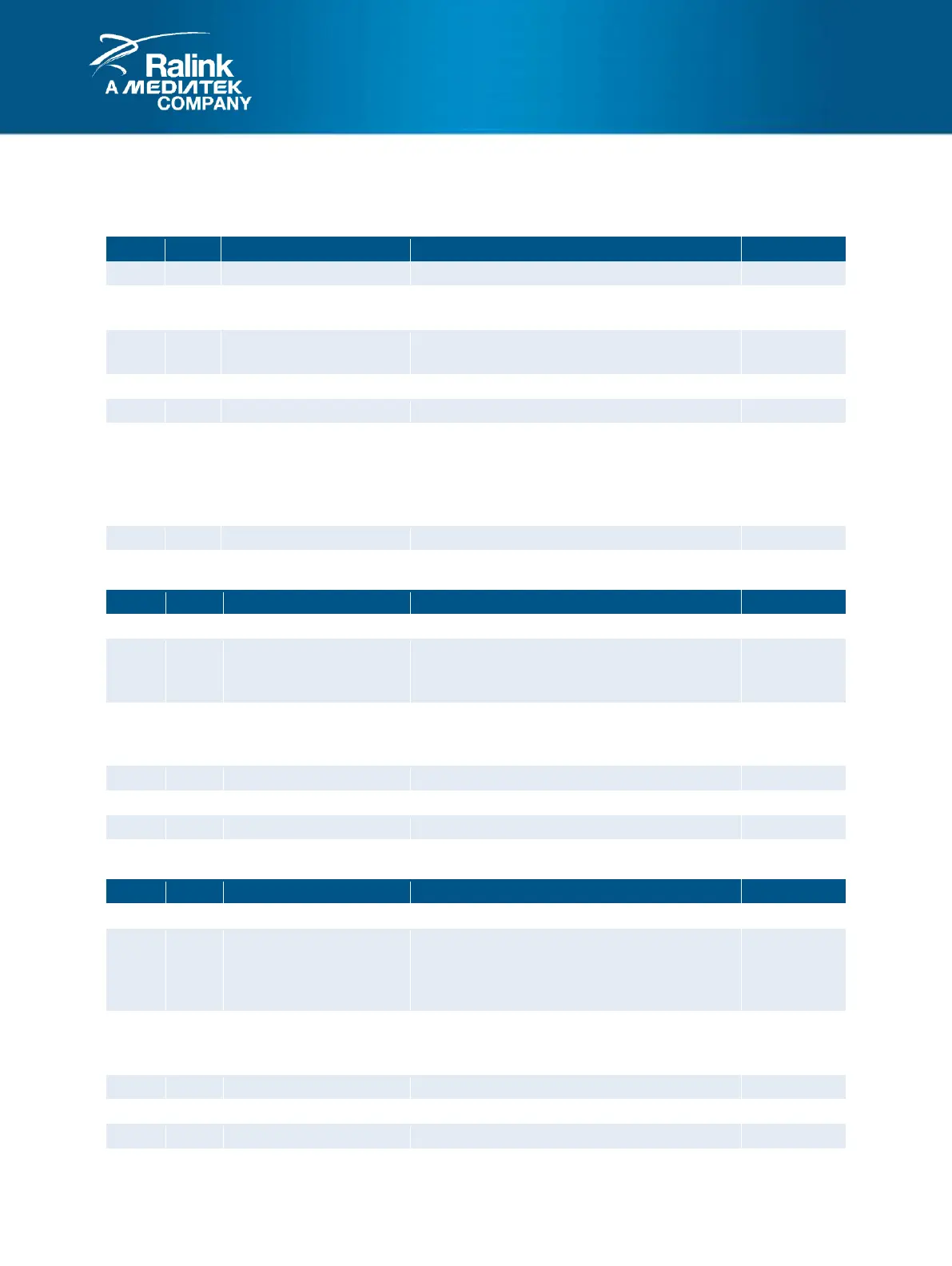

2.21.6.2 Register Descriptions

428. PCICFG: PCI Configuration and Status Register (offset: 0x0000)

Device number setting of Virtual PCI-PCI bridge

#1.

Device number setting of Virtual PCI-PCI bridge

#0.

PCI Reset Control

0: De-assert the PERST_N pin.

1: Assert the PERST_N pin.

This bit is set to 1 at chip reset.

(Available when PCIe Controller in Host mode)

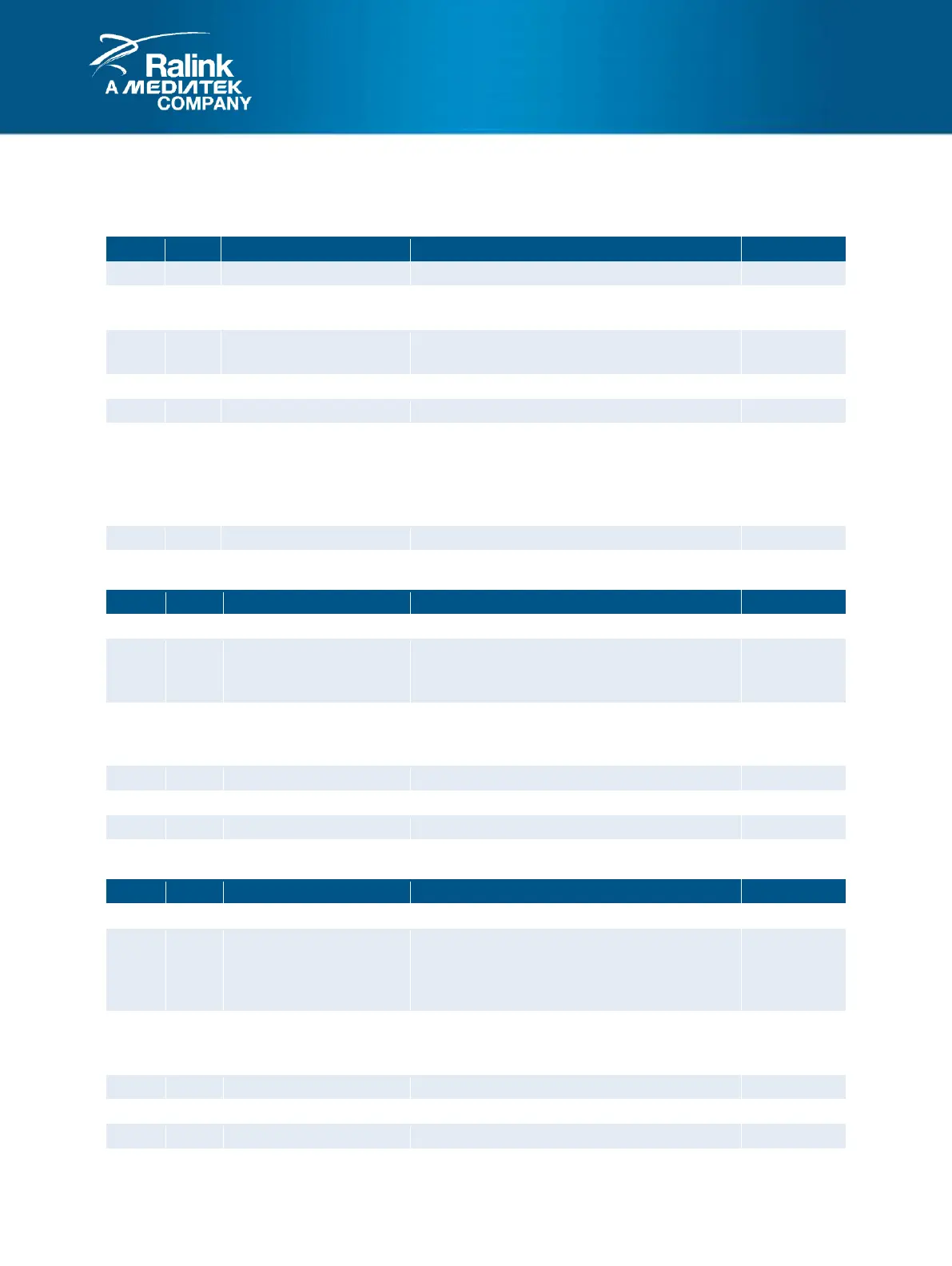

429. PCIINT: PCI Interrupt After Enable Mask (offset: 0x0008)

PCIe1 Interrupt Input in Host Mode

This bit indicates the PCIe interrupt from PCIe1

slot.

PCIe0 Interrupt Input in Host Mode

This bit indicates the PCIe interrupt from PCIe0

slot.

430. PCIENA: PCI Interrupt Enable (offset: 0x000C)

PCIe1 Interrupt Input in RC (Root Complex)

mode

0: Disable PCIe interrupt

1: Enable PCIe interrupt

PCIe0 Interrupt Input in RC Mode

0: Disable PCIe interrupt

1: Enable PCIe interrupt

Loading...

Loading...