MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

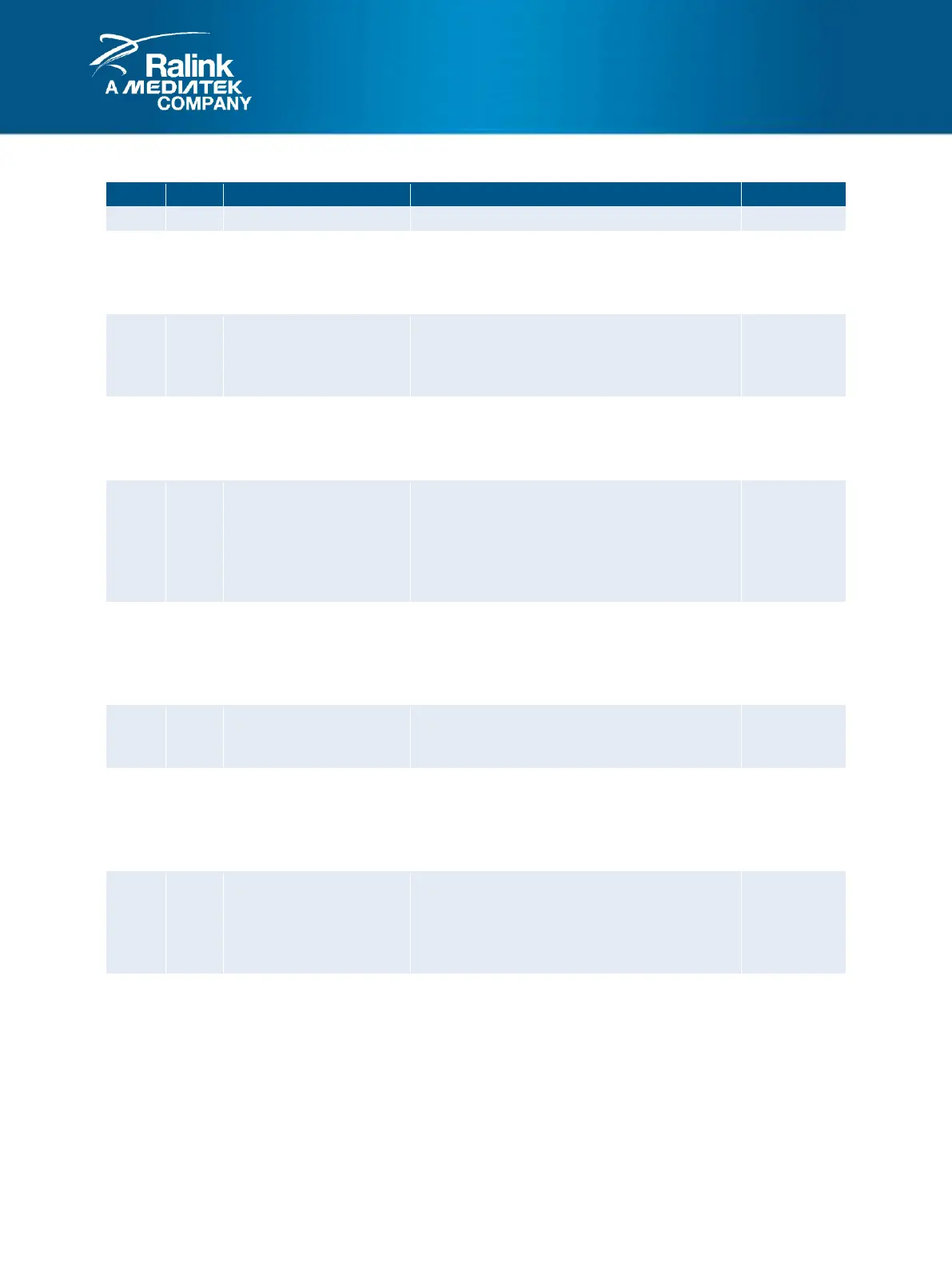

66. LSR: Line Status Register (offset: 0x001C)

Error in FIFO

Indicates that a FIFO contains data which was

received with a parity error, framing error, or

break condition.

Transmit Shift Register Empty

Indicates that the transmit shift register is

empty. This bit is reset when data is written to

the transmit buffer register (TBR).

Transmit Holding Register Empty

Indicates that the transmitter holding register is

empty. This bit resets when data is written to

the Tx buffer register (TBR).

Break Interrupt

Indicates that a break is received, that is, when

the RXD signal is at a low state for more than

one character transmission time (from Start Bit

to Stop Bit). Under this condition, a single 0 is

received.

Framing Error

Indicates that a valid Stop Bit is not detected. If

a framing error occurs, the receive buffer will

attempt to re-synchronize by sampling the Start

Bit twice and then receiving the data.

Parity Error

Indicates that the received parity is different

from the expected value.

Overrun Error

Indicates that when a receive overrun occurs.

This happens if a character is received before

the previous character has been read by

firmware.

Data Ready

Indicates that a character is received, and has

been transferred to the receive buffer register.

The bit is reset when all the characters are read

from the receive buffer register.

NOTE:

0: False

1: True

Loading...

Loading...