A-D Converter

M30240 Group

Rev.1.00 Sep 24, 2003 Page 102 of 360

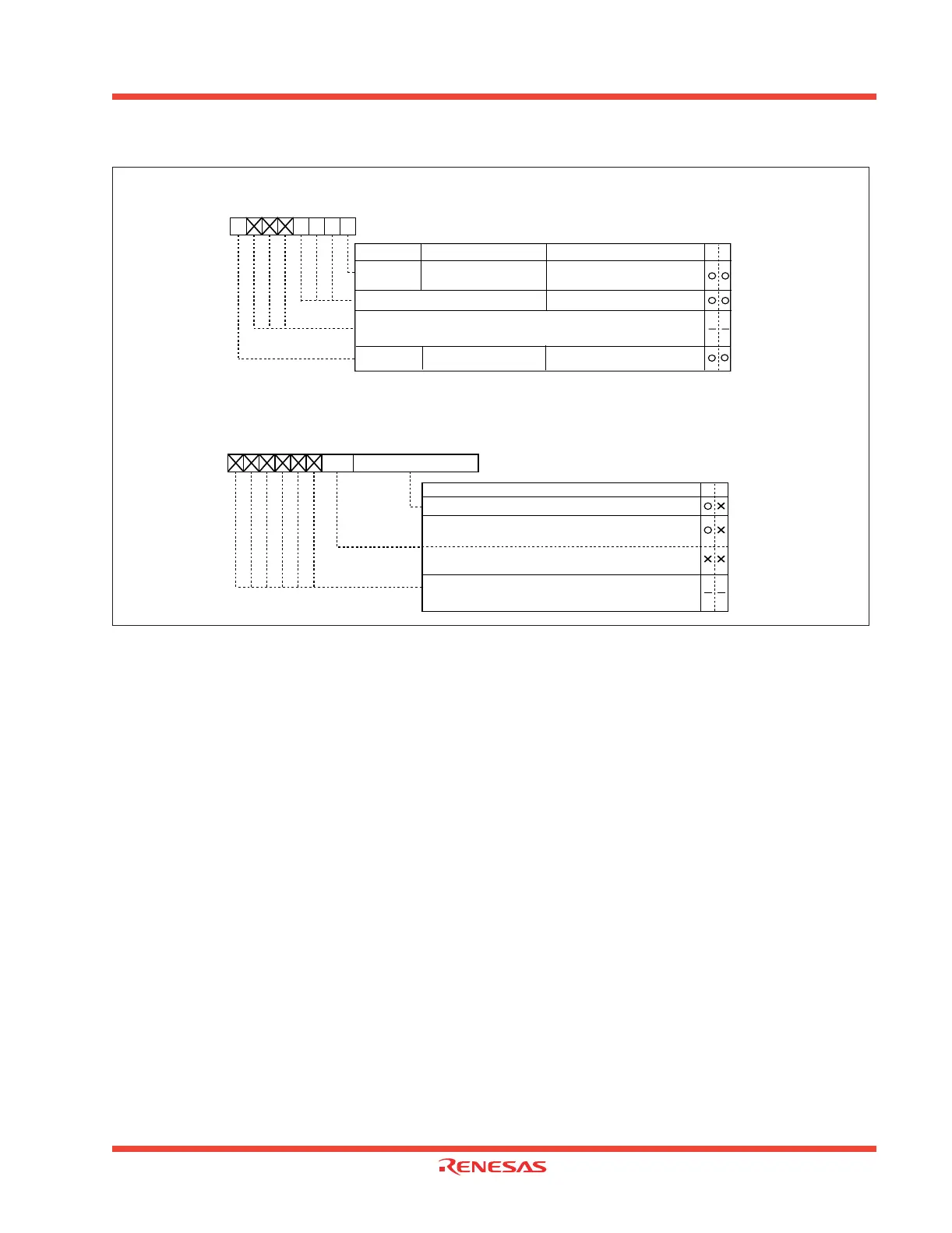

Figure 1.98: A-D converter-related registers (2)

A-D control register 2 (Note)

Symbol

Address

When reset

ADCON2 03D416

0000XXX0

2

b7 b6 b5 b4 b3 b2 b1 b0

A-D conversion method

select bit

0 : Without sample and hold

1 : With sample and hold

Bit symbol Bit name Function R W

Note : If the A-D control register is rewritten during A-D conversion, the conversion

result is indeterminate.

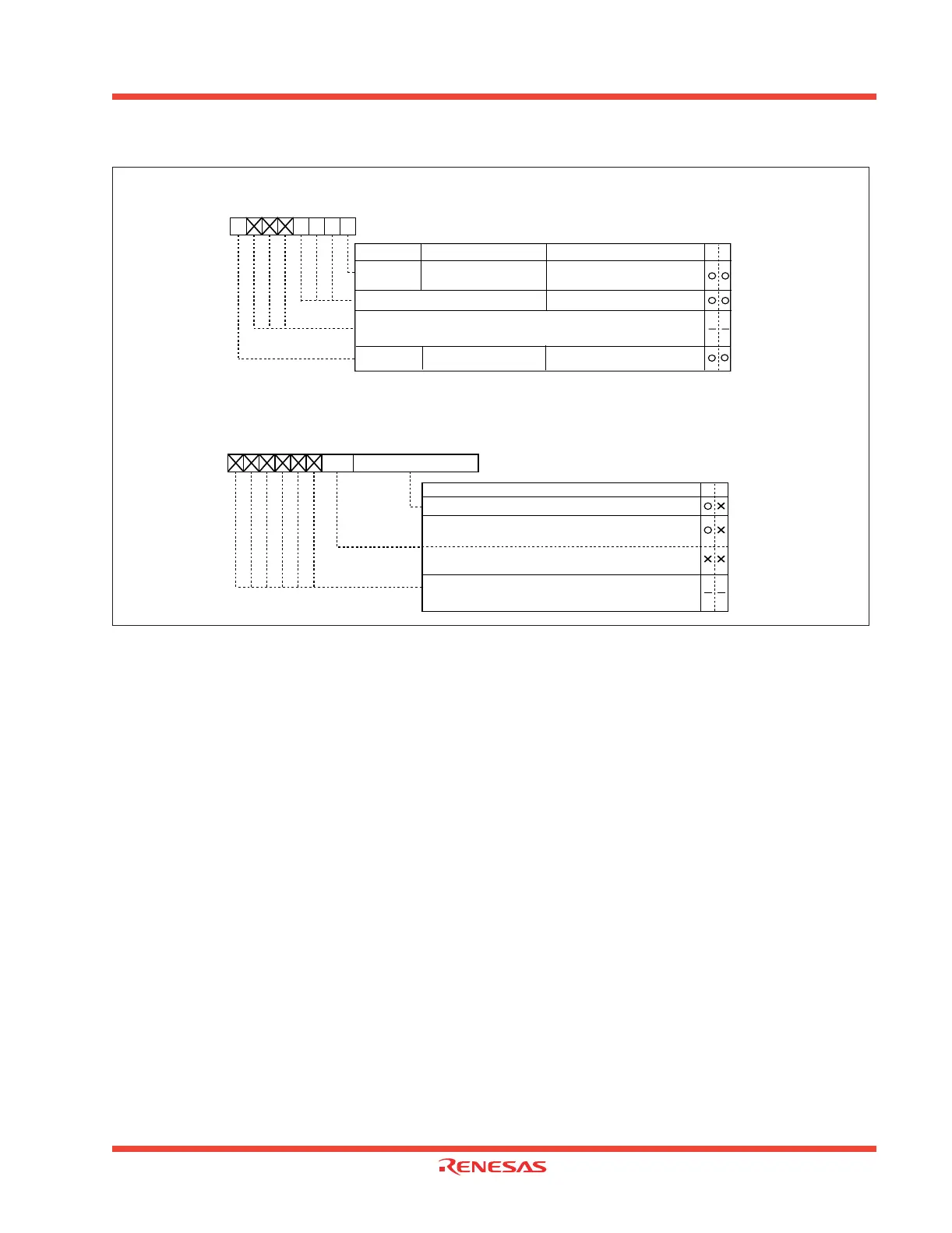

A-D register i

Symbol

Address When reset

ADi(i=0 to 7)

03C0

16

to 03CF

16

Indeterminate

Eight low-order bits of A-D conversion result

Function R W

(b15)

b7b7 b0

b0

(b8)

• During 10-bit mode

Two high-order bits of A-D conversion result

• During 8-bit mode

When read, the content is indeterminate

SMP

Reserved bit

Always set to “0”

000

SSH

Simultaneous sample and

hold

0 : Disabled

1 : Enabled

Nothing is assigned. Write "0" when writing to these bits.

When read, the value is "0".

Nothing is assigned. Write "0" when writing to these bits.

When read, the value is "0".

Loading...

Loading...