Clock-Synchronous Serial I/O

M30240 Group

Rev.1.00 Sep 24, 2003 Page 196 of 360

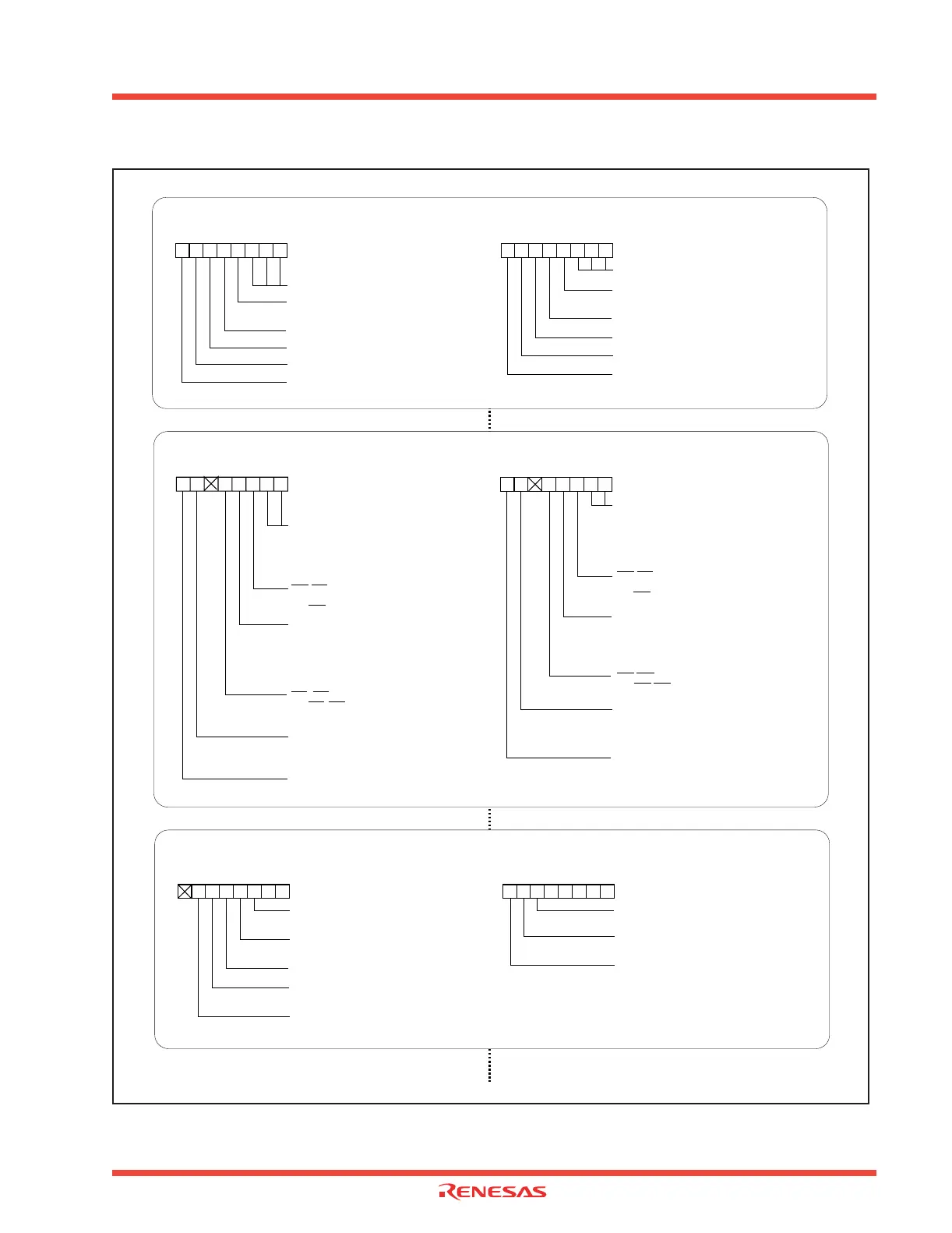

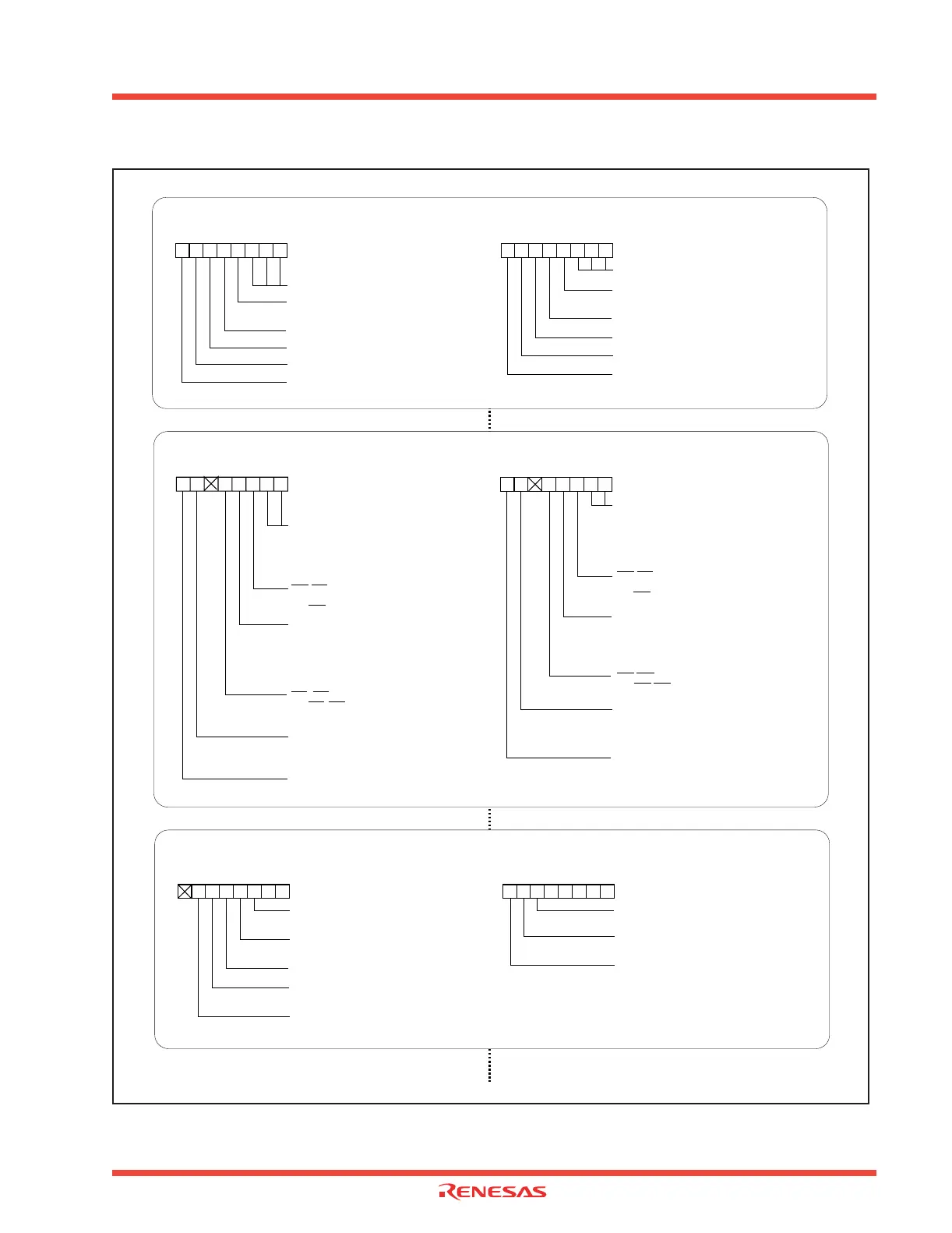

Figure 2.52: Set-up procedure of reception in clock-synchronous serial I/O mode (1)

Continued to the next page

Internal/external clock select bit

1 : External clock

Setting UARTi transmit/receive mode register (i=0 to 2)

UART0 transmit/receive mode register

U0MR

[Address

03A0

16]

UART1 transmit/receive mode register

U1MR

[Address

03A8

16]

Invalid in clock synchronous I/O mode

Must be fixed to “001”

b7 b0

01001

Invalid in clock synchronous I/O mode

Invalid in clock synchronous I/O mode

Sleep select bit

Must be “0” in clock synchronous I/O mode

Internal/external clock select bit

1 : External clock

UART2 transmit/receive mode register

U2MR

[Address 037816]

Invalid in clock synchronous I/O mode

Must be fixed to “001”

b7 b0

01001

Invalid in clock synchronous I/O mode

Invalid in clock synchronous I/O mode

T

X

D, R

X

D I/O polarity reverse bit

Usually set to “0”

Setting UARTi transmit/receive control register 0 (i=0 to 2)

UART2 transmit/receive control register 0

U2C0 [Address

037C

16]

CLK polarity select bit

0 : Transmission data is output at falling edge

of transfer clock and reception data is input

at rising edge

b7 b0

0100

CTS/RTS disable bit

0 : CTS/RTS function enabled

Transfer format select bit

0 : LSB first

UART0 transmit/receive control register 0

U0C0 [Address 03A4

16

]

UART1 transmit/receive control register 0

U1C0 [Address 03AC

16

]

CLK polarity select bit

0 : Transmission data is output at falling edge

of transfer clock and reception data is input

at rising edge

b7 b0

0100

BRG count source select bit

0 0 : f

1

is selected

0 1 : f

8

is selected

1 0 : f

32

is selected

1 1 : Inhibited

b1 b0

CTS/RTS function select bit

(Valid when bit 4 = “0”)

1 : RTS function is selected

CTS/RTS disable bit

0 : CTS/RTS function enabled

Transmit register empty flag

0 : Data present in transmit register

(during transmission)

1 : No data present in transmit register

(transmission completed)

Transfer format select bit

0 : LSB first

BRG count source select bit

0 0 : f

1

is selected

0 1 : f

8

is selected

1 0 : f

32

is selected

1 1 : Inhibited

b1 b0

CTS/RTS function select bit

(Valid when bit 4 = “0”)

1 : RTS function is selected

Transmit register empty flag

0 : Data present in transmit register

(during transmission)

1 : No data present in transmit register

(transmission completed)

UART transmit/receive control register 2

UCON [Address 03B0

16

]

UART0 continuous receive mode enable bit

0 : Continuous receive mode disabled

CLK/CLKS select bit 1

0 : Normal mode (CLK output is CLK1 only)

UART1 continuous receive mode enable bit

0 : Continuous receive mode disabled

Valid when bit 5 = “1”

b7 b0

00

Setting UART transmit/receive control register 2 and UART2 transmit/receive control register 1

UART2 transmit/receive control register 1

U2C1 [Address 037D

16

]

UART2 continuous receive mode enable bit

0 : Continuous receive mode disabled

Error signal output enable bit

Must be “0” in clock synchronous I/O mode

Data logic select bit

0 : No reverse

b7 b0

00

00

0

Reserved

Must always be "0"

Loading...

Loading...