DMAC

M30240 Group

Rev.1.00 Sep 24, 2003 Page 258 of 360

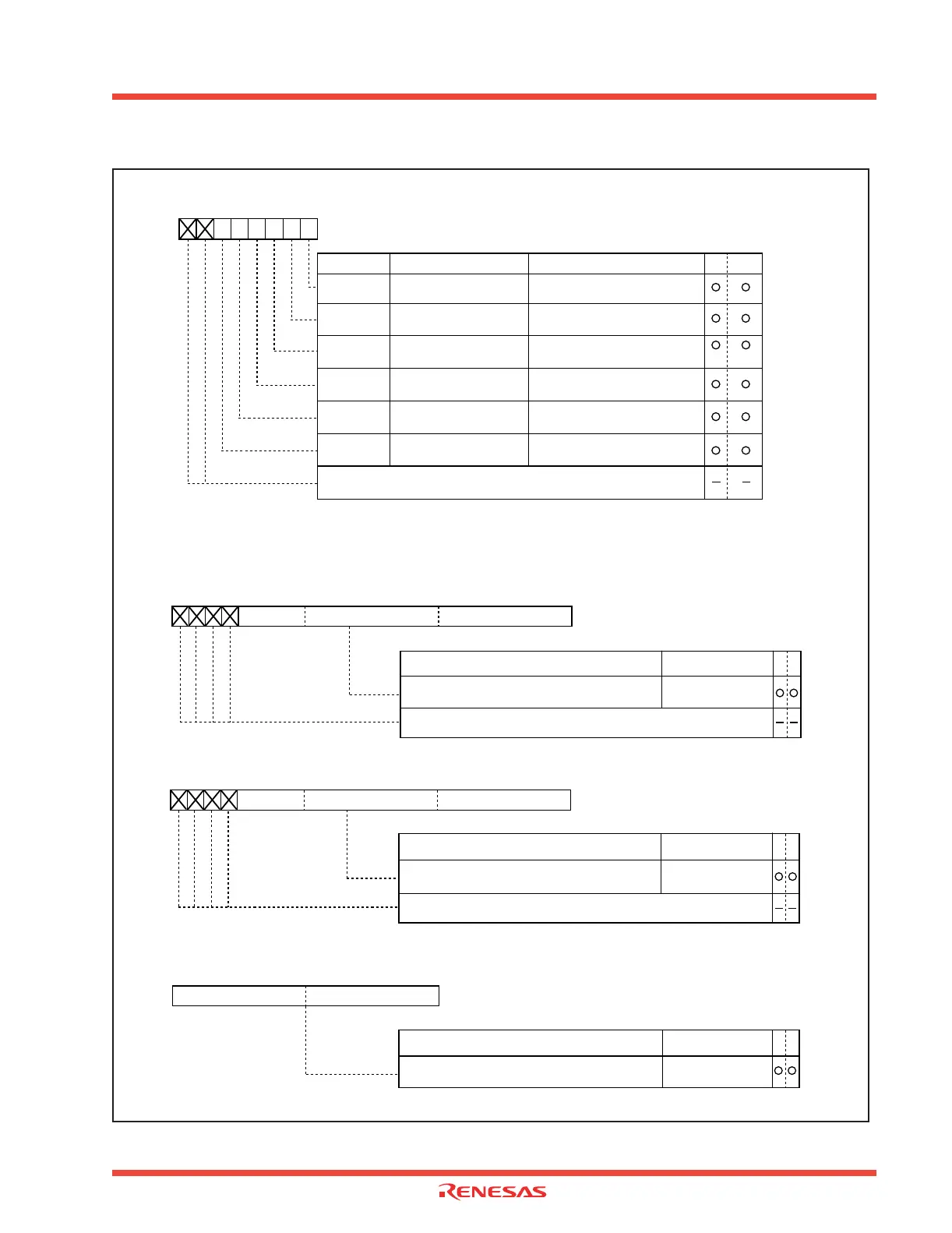

Figure 2.102: DMAC-related registers (2)

DMAi control register

Symbol Address When reset

DMiCON(i=0,1) 002C

16

, 003C

16

00000X00

2

Bit name FunctionBit symbol

Transfer unit bit select bit

b7 b6 b5 b4 b3 b2 b1 b0

0 : 16 bits

1 : 8 bits

DMBIT

RW

DMASL

DMAS

DMAE

Repeat transfer mode

select bit

0 : Single transfer

1 : Repeat transfer

DMA request bit (Note 1)

0 : DMA not requested

1 : DMA requested

0 : Disabled

1 : Enabled

0 : Fixed

1 : Forward

DMA enable bit

Source address direction

select bit (Note 3)

Destination address

direction select bit (Note 3)

0 : Fixed

1 : Forward

DSD

DAD

Nothing is assigned.

Note 1: DMA request can be cleared by resetting the bit.

Note 2: This bit can only be set to “0”.

Note 3: Source address direction select bit and destination address direction select bit

cannot be set to “1” simultaneously.

(Note 2)

(b23)

Symbol Address When reset

DAR0 0026

16

to 0024

16

Indeterminate

DAR1 0036

16

to 0034

16

Indeterminate

b7 b0 b7 b0

(b8)(b15)

Function

RW

• Transfer counter

Set a value one less than the transfer count

Symbol Address When reset

TCR0 0029

16

, 0028

16

Indeterminate

TCR1 0039

16

, 0038

16

Indeterminate

DMAi transfer counter (i = 0, 1)

Transfer count

specification

0000

16

to FFFF

16

b3 b0 b7 b0 b7 b0

(b8)(b15)(b16)(b19)

Function

RW

• Destination pointer

Stores the destination address

DMAi destination pointer (i = 0, 1)

Transfer count

specification

00000

16

to FFFFF

16

b7

(b23)

Nothing is assigned.

b7

b3 b0 b7 b0 b7 b0

(b8)(b16)(b15)(b19)

Function

RW

• Source pointer

Stores the source address

Symbol Address When reset

SAR0 0022

16

to 0020

16

Indeterminate

SAR1 0032

16

to 0030

16

Indeterminate

DMAi source pointer (i = 0, 1)

Transfer count

specification

00000

16

to FFFFF

16

Nothing is assigned.

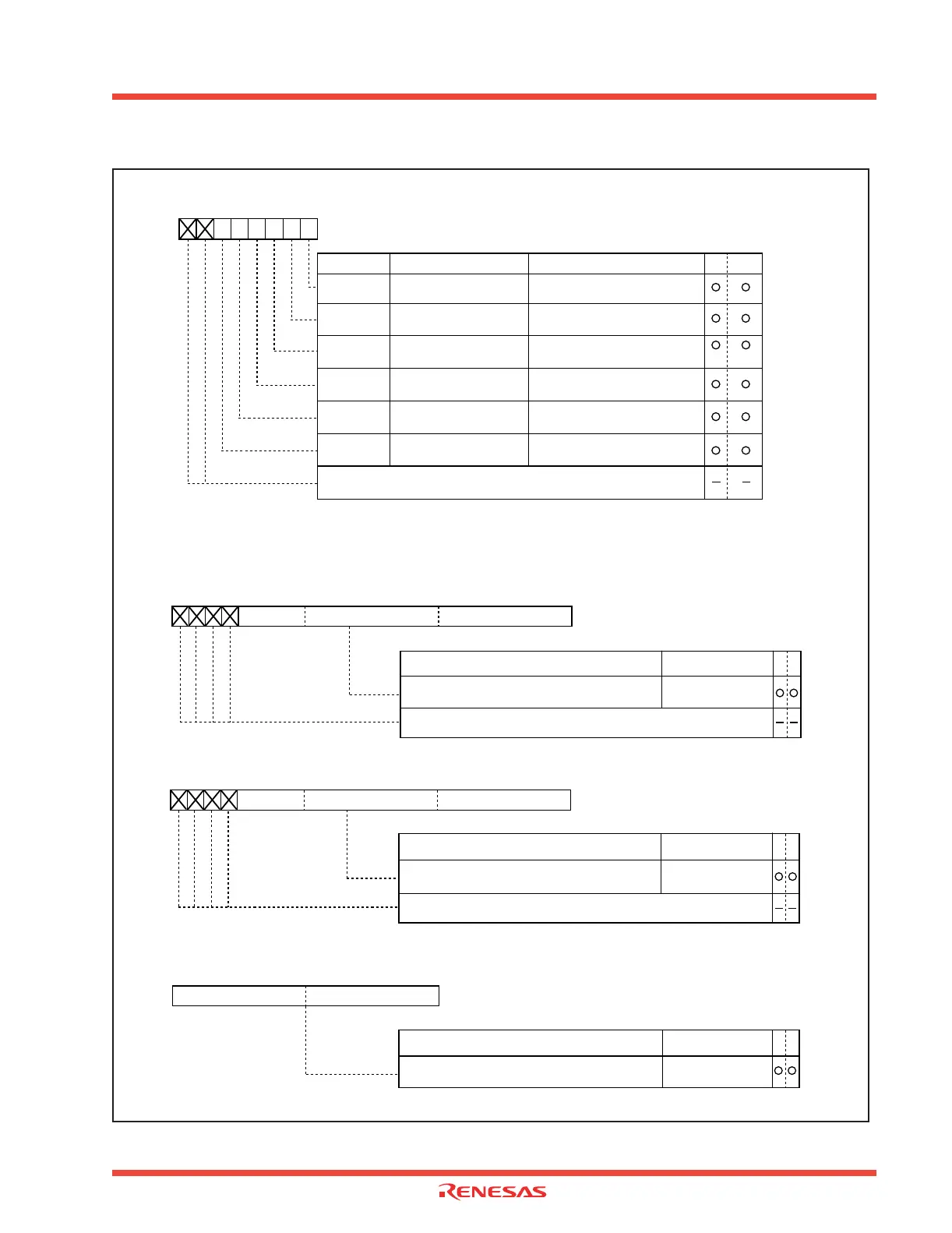

DMAi control register

Symbol Address When reset

DMiCON(i=0,1) 002C

16

, 003C

16

00000X00

2

Bit name FunctionBit symbol

Transfer unit bit select bit

b7 b6 b5 b4 b3 b2 b1 b0

0 : 16 bits

1 : 8 bits

DMBIT

RW

DMASL

DMAS

DMAE

Repeat transfer mode

select bit

0 : Single transfer

1 : Repeat transfer

DMA request bit (Note 1)

0 : DMA not requested

1 : DMA requested

0 : Disabled

1 : Enabled

0 : Fixed

1 : Forward

DMA enable bit

Source address direction

select bit (Note 3)

Destination address

direction select bit (Note 3)

0 : Fixed

1 : Forward

DSD

DAD

Nothing is assigned.

Note 1: DMA request can be cleared by resetting the bit.

Note 2: This bit can only be set to “0”.

Note 3: Source address direction select bit and destination address direction select bit

cannot be set to “1” simultaneously.

(Note 2)

(b23)

Symbol Address When reset

DAR0 0026

16

to 0024

16

Indeterminate

DAR1 0036

16

to 0034

16

Indeterminate

b7 b0 b7 b0

(b8)(b15)

Function

RW

• Transfer counter

Set a value one less than the transfer count

Symbol Address When reset

TCR0 0029

16

, 0028

16

Indeterminate

TCR1 0039

16

, 0038

16

Indeterminate

DMAi transfer counter (i = 0, 1)

Transfer count

specification

0000

16

to FFFF

16

b3 b0 b7 b0 b7 b0

(b8)(b15)(b16)(b19)

Function

RW

• Destination pointer

Stores the destination address

DMAi destination pointer (i = 0, 1)

Transfer count

specification

00000

16

to FFFFF

16

b7

(b23)

Nothing is assigned.

b7

b3 b0 b7 b0 b7 b0

(b8)(b16)(b15)(b19)

Function

RW

• Source pointer

Stores the source address

Symbol Address When reset

SAR0 0022

16

to 0020

16

Indeterminate

SAR1 0032

16

to 0030

16

Indeterminate

DMAi source pointer (i = 0, 1)

Transfer count

specification

00000

16

to FFFFF

16

Nothing is assigned.

Write "0" when writing to these bits. The value will be "0" when read.

Write "0" when writing to these bits. The value will be "0" when read.

Write "0" when writing to these bits. The value will be "0" when read.

Loading...

Loading...