RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1221

Dec 10, 2015

(2) LIN Slave Mode

(a) Types of Error Statuses

The LIN/UART module can detect seven types of error statuses in LIN slave mode [auto baud rate] or in LIN

slave mode [fixed baud rate]. These error statuses can be verified by checking the corresponding bits in the

LESTn register.

Table 17-17 shows the types of error statuses.

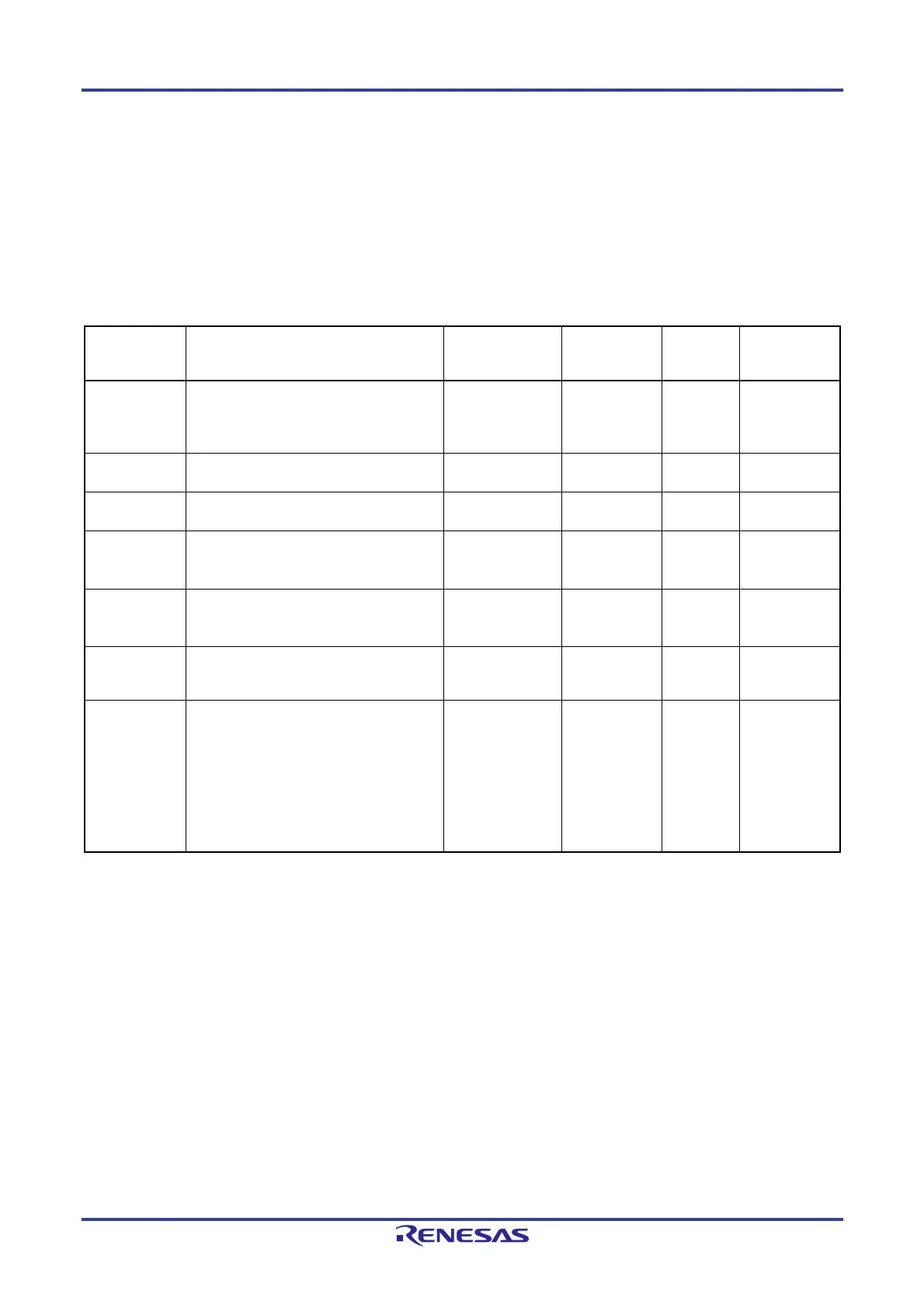

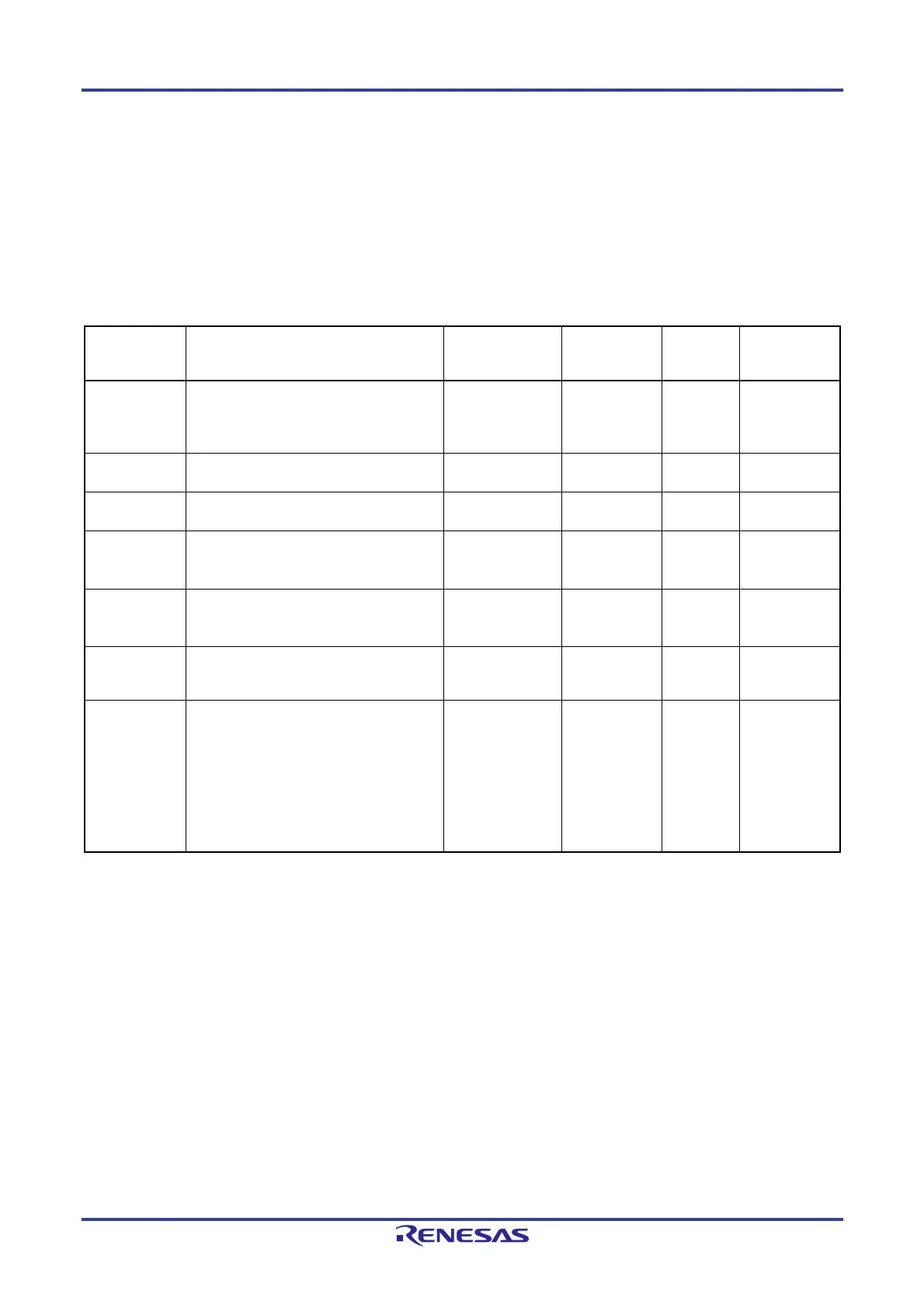

Table 17-17. Types of Error Statuses in LIN Slave Mode

Status Error detection condition

Operation mode

capable of error

detection

Communication

Enable/

disable

detection

Corresponding

bit

Bit error The transmitted data and the data on the

LIN bus monitored by the receive pin do not

match

Notes 1, 2

LIN operation

mode

LIN wake-up

mode

Cancel O

BER flag in

LESTn register

Timeout

error

A frame or response transmission/reception

does not terminate within a given time

Note 3

LIN operation

mode

Cancel O

TER flag in

LESTn register

Framing error In frame reception, a stop bit of each data

byte is low

LIN operation

mode

Cancel O

FER flag in

LESTn register

Sync field error If the width of the break low is greater than

the width set by the BLT bit in the LBFCn

register and the sync field is not 55H

LIN operation

mode

Cancel

O

Note 4

SFER flag in

LESTn register

Checksum error In response frame reception, the result of

checksum test gives an error

LIN operation

mode

—

Note 5

×

CSER flag in

LESTn register

ID parity error If the received ID parity bit does not match

the value that is automatically calculated by

the LIN/UART module

LIN operation

mode

Cancel O

IPER flag in

LESTn register

Response

preparation

error

After the reception of a header, before

the first reception data byte is received,

response preparation is not made in

time.

During a multi-byte response

transmission/reception, before the first

reception data byte of another data

group is received, preparation for

another data group is not made in time.

LIN operation

mode

Cancel ×

RPER flag in

LESTn register

Notes 1. If a bit error is detected, the process is canceled after a stop bit is sent. If a bit error is detected in a non-data

area, such as an inter-byte space, the transmission is canceled immediately after transmission of error bit. If

a bit error is detected during the transmission of a wake-up, the transmission of the wake-up is canceled after

the error-causing bit is sent.

2. In multi-byte response transmission, a bit error can be detected between data groups.

3. The timeout time depends on the response field data length (the RFDL[3:0] bits in the LDFCn register) and

the checksum selection (the LCS bit in the LDFCn register), and this can be calculated according to the

following formulae:

Until the RTS or LNRR bit in the LTRCn register is set, the timeout time is set based on 8-byte data. Once

the RTS bit is set, the timeout time is re-set based on the response field data length (the RFDL[3:0] bits in

the LDFCn register). When the LNRR bit is set, the timeout function is stopped.

[Frame timeout]

On classic selection (when the CSM bit in the LDFCn register is 0)

Timeout time = 49 + (number of data bytes + 1) × 14 [Tbit]

On enhanced selection (when the CSM bit in the LDFCn register is 1)

Timeout time = 48 + (number of data bytes + 1) × 14 [Tbit]

<R>

Loading...

Loading...