RL78/F13, F14 CHAPTER 23 STANDBY FUNCTION

R01UH0368EJ0210 Rev.2.10 1528

Dec 10, 2015

(2) HALT mode release

The HALT mode can be released by interrupt and reset signal generation.

(a) Release by unmasked interrupt request

When an interrupt request with an interrupt mask flag set to 0 (interrupt servicing enabled) is generated, the HALT

mode is released. If interrupt acknowledgment is enabled, vectored interrupt servicing is carried out. If interrupt

acknowledgment is disabled, the next address instruction of the HALT instruction is executed.

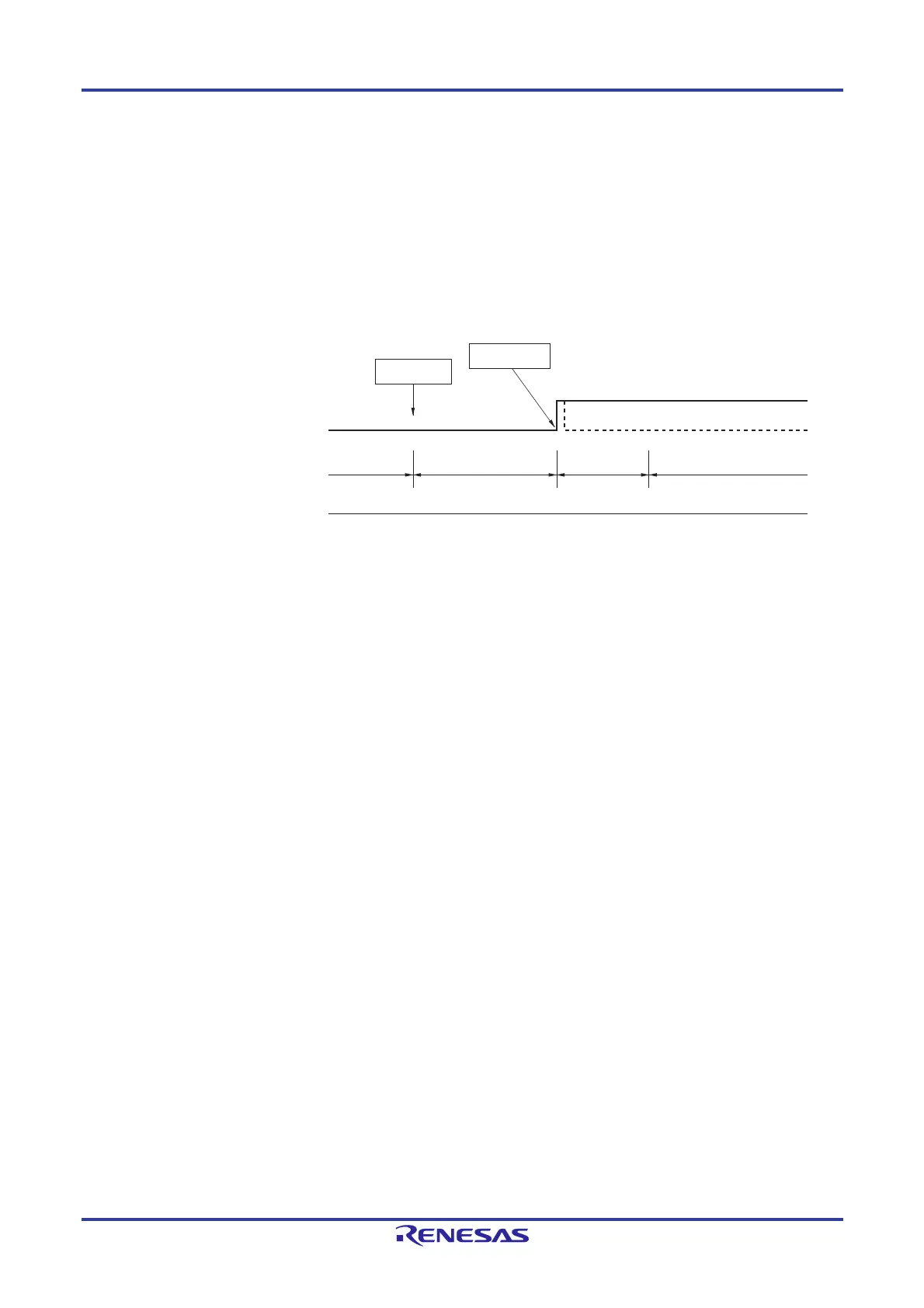

Figure 23-4. HALT Mode Release by Interrupt Request Generation

Note Wait time for HALT mode release

When vectored interrupt servicing is carried out

Main/PLL select clock: 15 to 16 clocks

Subsystem/low-speed on-chip oscillator select clock (RTCLPC = 0): 10 to 11 clocks

Subsystem/low-speed on-chip oscillator select clock (RTCLPC = 1): 11 to 12 clocks

When vectored interrupt servicing is not carried out

Main/PLL select clock: 9 to 10 clocks

Subsystem/low-speed on-chip oscillator select clock (RTCLPC = 0): 4 to 5 clocks

Subsystem/low-speed on-chip oscillator select clock (RTCLPC = 1): 5 to 6 clocks

Remark The broken lines indicate the case when the interrupt request which has released the standby mode is

acknowledged.

HALT

instruction

Operating modeHALT modeOperating mode

Oscillation

High-speed system clock,

High-speed on-chip oscillator clock,

PLL clock,

low-speed on-chip oscillator clock,

or subsystem clock

Status of CPU

Standby

release signal

Interrupt

request

Wait

Note

Loading...

Loading...