RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 160

Dec 10, 2015

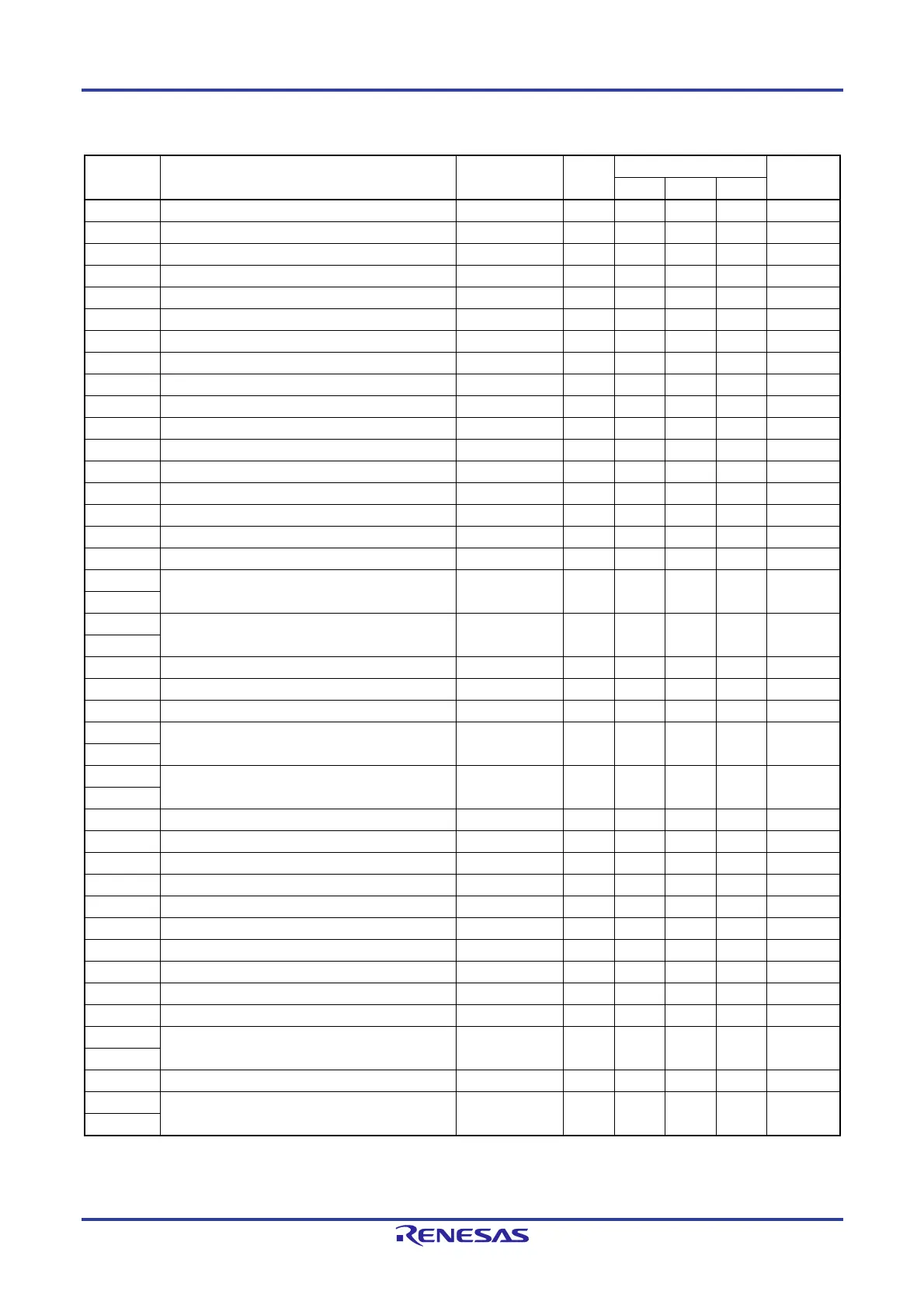

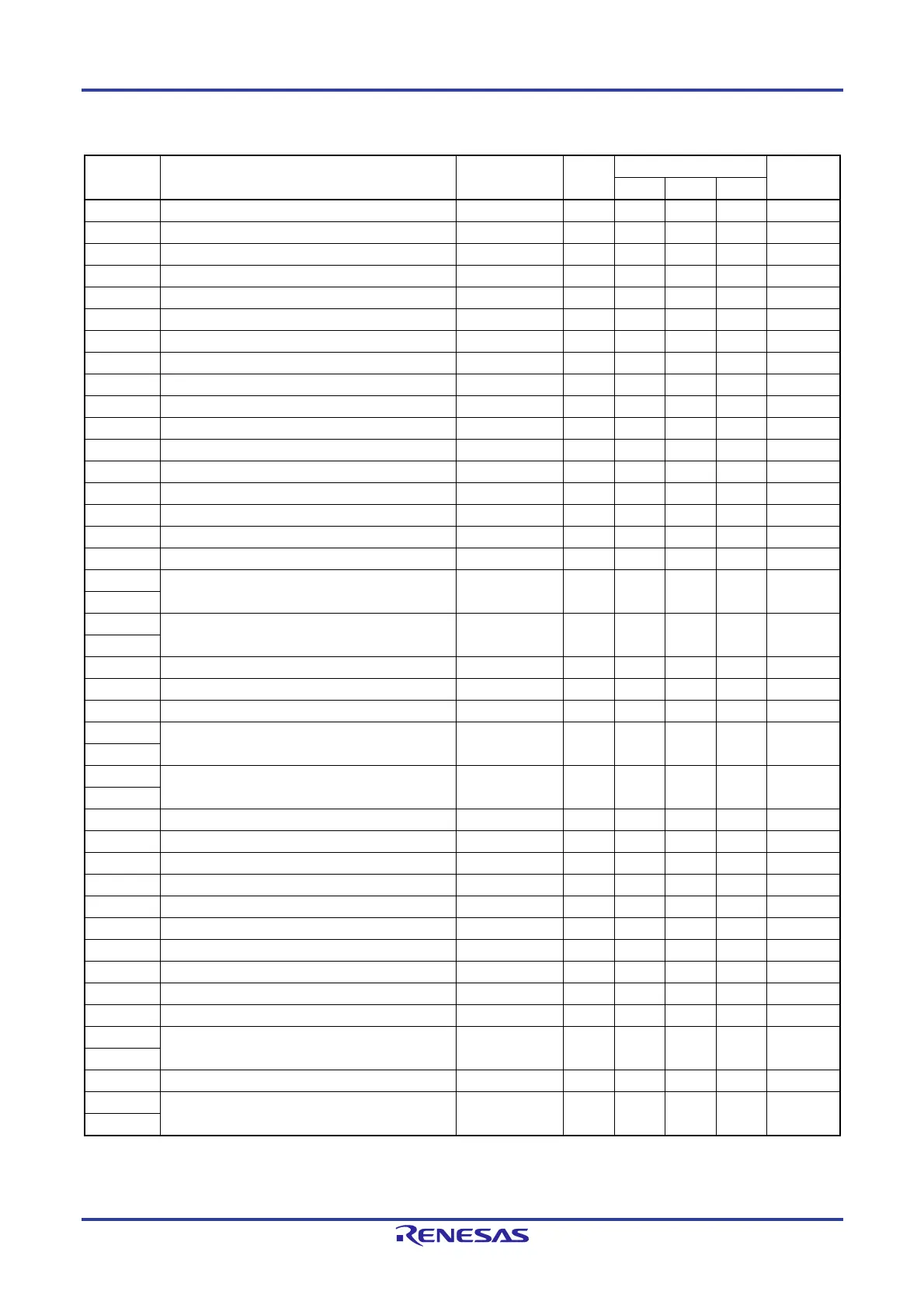

Table 3-6. Extended SFR (2nd SFR) List (9/32)

Address Special Function Register (2nd SFR) Name Symbol R/W Manipulable Bit Range After reset

1-bit 8-bit 16-bit

F02A0H Comparator control register CMPCTL R/W – 00H

F02A1H Comparator I/O switch register CMPSEL R/W – 00H

F02A2H Comparator output monitor register CMPMON R – 00H

F02C0H Peripheral enable register 1 PER1 R/W – 00H

F02C1H Peripheral enable register 2 PER2 R/W – 00H

F02C2H CAN clock select register CANCKSEL R/W – 00H

F02C3H LIN clock select register LINCKSEL R/W – 00H

F02C4H Clock select register CKSEL R/W – 00H

F02C5H PLL control register PLLCTL R/W – 00H

F02C6H PLL status register PLLSTS R – – 00H

F02C7H fMP clock division register MDIV R/W – – 00H

F02C8H RTC clock select register RTCCL R/W – 00H

F02C9H POR/CLM reset confirmation register POCRES R/W –

Note 1

F02CAH STOP status output control register STPSTC R/W – 00H

F02D0H High-speed DTC control register 0 HDTCCR0 R/W – 00H

F02D2H High-speed DTC transfer number register 0 HDTCCT0 R/W – 00H

F02D3H High-speed DTC transfer number reload register 0 HDTRLD0 R/W – 00H

F02D4H High-speed DTC source address register 0 HDTSAR0 R/W – – 0000H

F02D5H

F02D6H High-speed DTC destination address register 0 HDTDAR0 R/W – – 0000H

F02D7H

F02D8H High-speed DTC control register 1 HDTCCR1 R/W – 00H

F02DAH High-speed DTC transfer number register 1 HDTCCT1 R/W – 00H

F02DBH High-speed DTC transfer number reload register 1 HDTRLD1 R/W – 00H

F02DCH High-speed DTC source address register 1 HDTSAR1 R/W – – 0000H

F02DDH

F02DEH High-speed DTC destination address register 1 HDTDAR1 R/W – – 0000H

F02DFH

F02E0H DTC base address register DTCBAR R/W – – FDH

F02E1H High-speed DTC channel select register 0 SELHS0 R/W – 3FH

F02E2H High-speed DTC channel select register 1 SELHS1 R/W – 3FH

F02E8H DTC activation enable register 0 DTCEN0 R/W – 00H

F02E9H DTC activation enable register 1 DTCEN1 R/W – 00H

F02EAH DTC activation enable register 2 DTCEN2 R/W – 00H

F02EBH DTC activation enable register 3 DTCEN3 R/W – 00H

F02ECH DTC activation enable register 4 DTCEN4 R/W – 00H

F02EDH DTC activation enable register 5

Note 2

DTCEN5 R/W – 00H

F02F0H Flash memory CRC control register CRC0CTL R/W – 00H

F02F2H Flash memory CRC operation result register PGCRCL R/W – – 0000H

F02F3H

F02F9H CRC operation mode control register CRCMD R/W – – 00H

F02FAH CRC data register CRCD R/W – – 0000H

F02FBH

Notes 1. When a reset source other than POR occurs, bit 0 (the POCRES0 bit) retains a value right before reset.

2. Only in the RL78/F14.

Loading...

Loading...